# 一种高实时性的距离门控实现方法

范海波1,2,吴志波1,张海峰1,张忠萍1,陈菊平1

(1. 中国科学院上海天文台,上海 200030; 2. 中国科学院研究生院,北京 100049)

摘 要:给出了一种高实时性的距离门控实现方法,该方法基于高性价比的 Spartan-3 XC3S200 FPGA 芯片实现。相比传统的距离门控设计将距离门控计算放在计算机内进行,该方法把运算任务从计算机中抽调出来放在 FPGA 内部进行,最大程度地保证距离门控系统运行的高精度、高工作频率及高实时性。针对此方法的基本原理、运行流程及一些关键部分的实现作出了详细论述,如串口部分及其传输协议,乘法模块的实现以及大气后向散射的避免方法等。

关 键 词: 距离门; Sprtan-3 XC3S200; 高实时性; 高重复率卫星激光测距中图分类号: P228.5, TP319

### 1 引言

距离门控技术是一种时间滤波的技术,广泛应用于人造卫星激光测距系统中。其基本原理是根据预报参数,精确地计算出激光回波反射回来的预期时刻,采取稍微提前于预期的回波时刻开启回波接收系统的措施,最大程度避免背景噪声的干扰。

本文提出的距离门控方法可以用于低重复率的 SLR (Satellite Laser Ranging) 系统中,亦可满足高重复率 SLR 的要求。高重复率 SLR 是人卫激光测距的未来发展趋势,具有回波点数多、测距精度高等优点。传统的距离门控设计在低重复率情况下可以很好地工作,但随着 SLR 向更高的测距频率方向发展,对距离门控的要求也更高,传统设计已难以适应。

首先,距离门控精度问题。在高重复率 SLR 中,噪声数远比低重复率 SLR 多,高精度距离门控有利于抑制噪声,提高测距成功率。而传统的设计多采用分立元器件,距离门控精度有限,难于适应越来越高频率的 SLR 系统。其次,系统的实时性问题。传统距离门控设计中距离门控的计算在计算机中进行,然后通过相应的接口传送到距离门控电路。随着测距频率的提高,控制软件的单次测距时间被缩短,大量的数据运算及传送将占用原本就紧张的 CPU资源,降低控制软件的实时性,甚至导致测距失败。再次,在高重复率 SLR 中存在大气后向散射干扰问题,造成有效回波信号的损失。散射的发生时序与激光点火时序和距离门控信号时序相关,后向散射在低重复率 SLR 中没有影响,因此传统的距离门控设计也不具备后向散射避免功能。

针对以上3个主要问题,本文介绍了一种高实时性距离门控实现方法。该方法主要是将距离门控计算的核心部分移至FPGA芯片内部,以减轻测距计算机的负担,进而提高高重复率激光测距的实时性。

收稿日期: 2010-07-13; 修回日期: 2010-08-11

资助项目: 国家自然科学基金 (10973029); 上海市空间导航与定位技术重点实验室 (06DZ22101)

# 2 距离门控计算方法

在卫星激光测距过程中,距离门控的计算实质上是根据卫星预报数据预计激光信号的往返飞行时间,即卫星到测距站的双程距离值,以确定光子探测器的打开时刻,进而准确地接收回波光子,实现卫星测距。在卫星预报中,为减少预报过程中的数据量及计算量,我们在预报数据中只给出了间隔为 1 s (近地卫星) 或 20 s (远地卫星) 的卫星距离预报值。而在测距过程中,间隔 1 s 或 20 s 的预报数据密度是不能满足实时测距控制要求的,为此,在获得间隔 1 s 或 20 s 的预报数据后,我们采用了多项式拟合的方法,每 4 个预报数据组合成一组三阶多项式,如式 (1) 所示,其中  $R_0,R_1,R_2,R_3$  分别为卫星距离预报值, $t_0,t_1,t_2,t_3$  分别为卫星距离对应的时刻值。

$$\begin{cases}

R_0 = a_0 + a_1(t_0 - t_0) + a_2(t_0 - t_0)^2 + a_3(t_0 - t_0)^3 \\

R_1 = a_0 + a_1(t_1 - t_0) + a_2(t_1 - t_0)^2 + a_3(t_1 - t_0)^3 \\

R_2 = a_0 + a_1(t_2 - t_0) + a_2(t_2 - t_0)^2 + a_3(t_2 - t_0)^3 \\

R_3 = a_0 + a_1(t_3 - t_0) + a_2(t_3 - t_0)^2 + a_3(t_3 - t_0)^3

\end{cases}$$

(1)

通过求解方程组 (1) 获得多项式系数  $a_0, a_1, a_2, a_3$ 。在距离门控计算中,应用多项式系数,由公式 (2) 实时获得卫星距离预报值,进而获得激光信号的往返飞行时间。式 (2) 中 j 表示所使用的为第 j 组系数, $t_i$  为第 j 组系数内计算的第 i 次卫星距离预报值  $R_i$  对应的时刻。公式 (2) 中的  $t_i - t_0$  也可记为  $\mathrm{d}t_i$ 。

$$R_i = a_{i0} + a_{i1}(t_i - t_0) + a_{i2}(t_i - t_0)^2 + a_{i3}(t_i - t_0)^3$$

(2)

实际上, $R_i$  为时间量。设距离门控开启时刻为  $S_i$ ,计时零点为  $t_0$ ,提前开启量为  $a_p$ ,则计算可进一步简化为:

$$S_i = R_i + (t_i - t_0) - a_p . (3)$$

# 3 Spartan-3 XC3S200 简介

本设计的核心部分采用 Xilinx 公司的 Spartan-3 XC3S200 芯片来完成。Spartan-3 XC3S200 芯片是一款低成本的 FPGA 芯片,它基于前 4代 Spartan 系列解决方案的基础之上,把 Xilinx 高端 Virtex 系列的一些特性集成其中,并较 Spartan-2 系列具有更多的逻辑资源、内部 RAM 容量和 IO 数。

该芯片拥有 150 万的逻辑门编程资源,完全满足本设计的空间要求; 拥有自带的数字时钟管理 (DCM),倍频速度可以达 200 MHz 以上,即能保证系统的运行精度在 5 ns 以内; 自带 12 个 18 位×18 位的嵌入式硬件乘法器,理论运行速度可达到每秒上万亿次,在单脉冲触发时间内完全可以进行单次乘法运算,满足设计所需的速度要求; 18 KB 块 RAM,可以用做缓存或高速缓存,在本设计中,被用于生成 FIFO 序列。另外,由 Xilinx 公司提供的 FPGA 开发软件 ISE 自带的 IP 软核,可以有效支持 Spatran-3 系列芯片合成内部自带的硬件资源,生成可满足设计要求的高位乘法器模块和大容量 FIFO 序列模块。

## 4 设计原理

#### 4.1 基本原理图

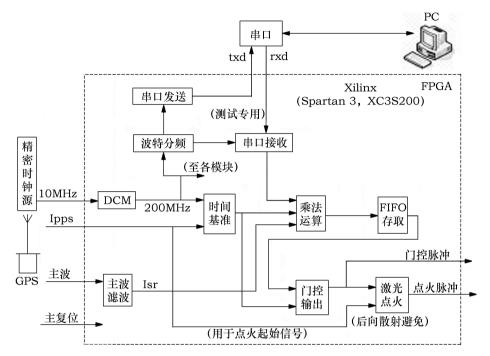

基于 Spartan-3 设计的距离门控实现基本原理图如图 1 所示。

图 1 距离门控原理图

#### 4.2 运行流程详细描述

如图 1 所示,系统总共有 5 个输入信号和 3 个输出信号。其中,输入信号为 10 MHz 的外部精准时钟源信号,GPS 精准秒脉冲信号 Ipps、激光主波信号、串口输入信号 rxd 和总复位信号 rst,而输出信号为距离门控开启脉冲信号、激光点火脉冲信号以及串口发送信号 txd。

10 MHz 信号输入,经过内部的 DCM 模块倍频至 200 MHz 方波信号后,作为系统时钟,提供给系统内部各数字电路部分使用; Ipps 信号则作为一个时钟基准同步信号,使得系统内部的时钟基准模块,精确同步于整个 SLR 系统的 GPS 运行时钟。

计算机以  $1 \, \mathrm{s}$  为周期,向门控板发送  $4 \, \mathrm{f}$  令数  $a_{j0}, a_{j1}, a_{j2}, a_{j3}$ ,串口接收模块负责接收这些参数。以  $\mathrm{Ipps}$  信号为周期  $1 \, \mathrm{s}$  时间段的分界点,在第  $(j-1) \, \mathrm{s}$  内,计算机预先发送第  $j \, \mathrm{s}$  需要使用的参数。因此,先前接收完全的参数必须经过锁存,并且等待。当  $\mathrm{Ipps}$  信号触发至第  $j \, \mathrm{s}$  时,才将这些被暂存的参数更新至乘法模块。此举是考虑到参数的接收需要一定的时间,而在这段时间内,乘法模块依旧需要完整的参数输入值。

在第js时,乘法模块进行主波的响应并进行运算,得到距离门控开启时刻。乘法模块以内部时钟基准模块提供的基准时钟为准,当第i个主波信号  $lsr_i$  (此处主波信号  $lsr_i$  已经过主波滤波模块的滤波,相关的滤波措施根据系统的实际情况而定,在此不做详细讨论)到来时,获取主波到来时的精准时刻  $dt_i$  (在此,由于 $t_0$  为时钟基准模块的起点时刻,即 $t_0=0$ , $dt_i=t_i-t_0$ ),并且以使能信号的形式启动乘法模块的运算,得到当前主波  $lsr_i$  对应

的卫星距离预报值  $R_i$  以及距离门控开启时刻  $S_i$ 。

需要说明的是,由于基准时间的周期为 1 s,而实际计算得到的  $S_i$  的取值范围总在  $0\sim2$  s 之间,如果  $S_i$  大于 1,将超过基准时间的周期,无法计数比较。为此,在计算完后则立即进行比较,如果  $S_i$  大于 1,则减去 1,完成上述计算后,即刻产生一个使能信号,将  $S_i$  存入 FIFO中,如此可保证 FIFO中存储的值始终在  $0\sim1$  之间变动。

在主波产生后的  $1 \, \mathrm{s}$  内  $S_i$  对应的基准时刻,得到相应的距离门控脉冲的输出。先前计算得到的  $S_i$  值对应的时刻不会马上到来,而后续的计算依然进行。因此需要先存储,等到时间基准模块运行至  $S_i \, \mathrm{s}$  时,才可以输出距离门控开启脉冲信号。此功能由系统中的 FIFO 模块完成。在此,简略描述 FIFO 的调用规则。若 FIFO 中先前没有数据,则将乘法模块的计算结果存入后,立即产生相应的 FIFO 调出,作为门控输出模块的输入使用;若 FIFO 中先前已经存有数据,则在一个门控开启脉冲产生后,即刻调用下一个数据,作为下一个门控开启脉冲信号产生的时刻值,提供给门控输出模块使用。

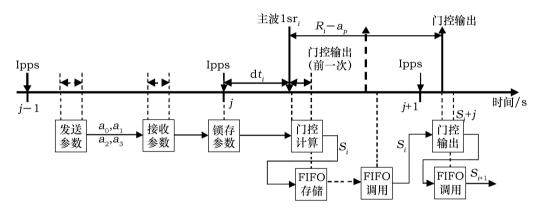

为了便于理解,给出一个简略的时序及数据流图,如图 2 所示。

图 2 距离门控实现时序及数据流图

在图中,仅对一个主波以及对应的门控输出进行讨论。将第 j个 Ipps 信号发生的时刻 (即第 j s) 记为一次零点,主波发生的时刻则为  $dt_i$ ,计算得到的对应的门控输出时刻为  $S_i$ ,在时序图中对应的时刻则为  $S_i+j$ ,主波和门控输出中间的时间差则为  $R_i-a_p$ 。图中亦有一个虚线表示的前一次门控输出,以说明在非空的情况下,FIFO 的调用发生在紧接上一个门控输出之后。

# 5 关键技术的实现原理

#### 5.1 串口传输及协议

设计采用的 RS232 是一种异步串行通信接口,协议较简单、使用广泛。电路干扰会使数据的边缘采样发生误判,在数据中央采样时其出错概率最低,因此数据采样率一般都是波特率的数倍频。本电路波特率为 38 400,8 倍频采样 (即在一个 38 400 波特脉冲内有 8 个均等的子脉冲)可以使误码率最小。时钟为 200 MHz,200 000 000/651=38 400×8,误码率仅为 0.000 1%,基本不可能产生错误的数据值。

在本设计中,为了充分有效地利用串口采样的中央值,采用前6个脉冲进行采样,第7

个脉冲进行串口位的判断,当6次采样中5次正确时,则在第8个脉冲暂存正确的串口数据位 (即实际被认可的串口电平位),并由波特率为38400的脉冲进行实际的串口数据接收。

一次有效串口数据传输为 10 位二进制,设定了起始位和停止位,中间 8 位为有效数据位。每隔 1 s 的时间由计算机向 FPGA 发送计算所需的参数  $a_0, a_1, a_2, a_3$ ,每一个参数由 48 位有符号位组成,总计为 192 位,合成一次数据包。数据包的包头设定 8 位指定的起始字节,包尾同样设定 8 位结束字节。当起始字节和结束字节均判断正确时,则表示一次数据接收正确,更新系统锁存的参数。否则,放弃本次数据包,系统在下一时刻仍调用当前数据而不进行更新。

#### 5.2 乘法运算及分析

该部分为整个设计的核心部分。根据系统所需精度的要求,设计一个 48 位×18 位的有符号乘法器,总计用到 3 个 Spartan-3 自带的 18 位×18 位乘法器。乘法器是并级连接,由脉冲上升沿触发,因此,在一个内部时钟内,可以完成规定的一次乘法运算。以下给出乘法模块的设计及运算原理。

由第2节已知,公式(3)写成形式:

$$S_i = a_0 + a_1 \cdot dt + a_2 \cdot (dt)^2 + a_3 \cdot (dt)^3 + dt - a_p.$$

(4)

具体运算时,可以将此公式分解为公式(5)的形式,依据由内向外、先乘再加的准则来进行。

$$S_i = ((a_3 \cdot dt + a_2) \cdot dt + a_1) \cdot dt + a_0 + dt - a_p$$

(5)

$a_0, a_1, a_2, a_3$  的 4 个参数值的原始单位为 10 ns,且形式为小数,实际上,由串口直接传送过来的数据是经过移位处理的,单位为 1 ns,且去掉了小数部分。dt 为一个小于 1 s 的小数,然而,实际上时间格式为计数器形式的整数,系统时钟频率为 200 MHz,最大计数值也即  $2\times10^8$ 。因此,需要除法运算将计数器值转化为真实时间的形式。

由于 FPGA 内部自带的只有专用硬件乘法器,而没有专门的除法运算模块,在此,用乘法运算来近似实现除法运算的功能。充分考虑到精度要求和实际可用的乘法器资源,参考式(6)可得近似的计算值,该等式误差率仅为 10<sup>-8</sup> 数量级。

$$dt = \frac{cnt}{2 \times 10^8} \approx \frac{1407375 \cdot cnt}{2^{48}} \tag{6}$$

因此,可以将公式(5)的运算,进一步描述为:

$$S_i = \left( \left( a_3 \cdot cnt \cdot \frac{1\,407\,375}{2^{48}} + a_2 \right) \cdot cnt \cdot \frac{1\,407\,375}{2^{48}} + a_1 \right) \cdot cnt \cdot \frac{1\,407\,375}{2^{48}} + a_0 + \frac{1\,407\,375}{2^{48}} - a_{\rm p} \; . \tag{7}$$

运算共分为 4 步进行,第 1 步先计算 *cnt* 与时间常数 1 407 375 的乘法值,并将此值作为一个新时间常数进行后续的运算。后 3 步为该新时间常数与参数的乘法,以及相应的加减法运算,且每次相乘后,直接以二进制形式截去乘法器模块结果寄存器的第 48 位 (在公式中表现为除以 2<sup>48</sup>),得到与用真实时间直接计算所得相似的数值。

理论分析表明,经过以上变换处理,实际所得结果误差不会超过5ns。用一组实际的参数进行验证,所得实际运算结果和先验运算结果仅相差1ns,完全符合精度的要求。

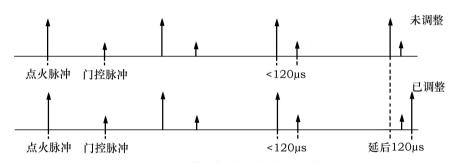

#### 5.3 后向散射的避免

后向散射指在少数情况下,当某次回波信号即将到达望远镜时,光子探测器的距离门控已经打开,若此时正值一个激光脉冲发射出去,则此脉冲产生的大气后向散射信号会进入光子探测器,产生严重的干扰,引起测距的失败。理论分析表明,在高重复率激光测距系统中(如激光点火频率为2kHz),会有较大的概率遇到后向散射。这里讨论,在不变动距离门控已定时刻及其脉冲的情况下,通过调整激光点火脉冲时刻,避免后向散射的问题。

本设计规定,在当前激光点火时刻之后的  $120\,\mu s$  时间内,如果有距离门控脉冲信号发生,则将下次激光点火的发生时刻延后  $120\,\mu s$ 。后向散射产生的原理及预防机制可参考图 3。

图 3 上半部分为未调整的激光点火脉冲和门控脉冲关系示意图。可以看出,一旦门控脉冲进入了后向散射发生区域 (<120  $\mu$ s),后续的一系列门控脉冲都有可能进入该区域,造成后向散射的问题。问题的解决方案如图 3 的下半部分所示。当发生了后向散射时,激光点火信号则自动延迟 120  $\mu$ s 的时间,从而使得之后一系列点火时刻都和门控时刻相错,而避免了该问题。

图 3 后向散射机制及避免措施示意图

## 6 仿真验证措施

程序代码统一经过 Modelsim 软件仿真并得到第一步验证,仿真通过后,则在一块已有的 FPGA 试验用 PCB 板上进行实际电路的调试及验证。该 PCB 板除拥有设计所需的 Spartan-3 芯片以外,还带有实际所需的各信号接口(如串行口、时钟源接口等)。

各模块的数据统一通过串口发送模块回送给计算机来进行验证。以8位为1个字节,附加起始位0和结束位1,采用38400的波特率进行发送。通过增加串口发送模块的接口以及修改发送寄存器中的数值,可以方便地验证所有模块的数据。实际上,可通过暂时修改各待验证模块的代码、增加虚拟量的方法,对各模块的功能逐一验证,具体不在此赘述。

串口验证数据发送的基本格式如表 1 所示,其中,数字代表串口发送寄存器中各值的位数。以 Ipps 信号为触发将该组数据进行发送。计算机中,同样以此格式显示并进行观察。

| 数据     | $a_0, a_1, a_2, a_3$ | 点火频率值   | 主波时刻值   | 乘法输出值   | FIFO 输出值 |

|--------|----------------------|---------|---------|---------|----------|

| 格式 /位数 | 0-191                | 192-219 | 224-252 | 256-286 | 288-318  |

表 1 串口验证数据发送格式

# 7 小 结

本文介绍了一种高实时性的距离门控实现方法,该方法充分调用了 Spartan-3 XC3S200 FPGA 芯片的性能,最大程度上保证了系统的高精度、高工作频率和高实时性。本文就该方法的设计原理及运行流程作了详细的论述,并给出了关键技术的实现原理以及相关的仿真验证措施。研究表明,该方法可以投入到实际应用中。

#### 参考文献:

- [1] 吴志波. 硕士论文. 上海: 中国科学院上海天文台, 2006: 4

- [2] 张忠萍, 吴志波, 张海峰等. 激光与红外, 2009, 39(12): 12

- [3] Spartan-3 FPGA Family Data Sheet. XILINX. DS099 December 4, 2009

- [4] 夏宇闻. Verilog数字系统设计教程. 北京: 北京航空航天大学出版社, 2004: 45

# A Method of Realization of Range Gate Generator with High Realtime

FAN Hai-bo<sup>1,2</sup>, WU Zhi-bo<sup>1</sup>,

ZHANG Hai-feng<sup>1</sup>, ZHANG Zhong-ping<sup>1</sup>, CHEN Ju-ping<sup>1</sup>

Shanghai Astronomical Observatory, Chinese Academy of Sciences, Shanghai 200030;

Graduate School of Chinese Academy of Sciences, Bejing 100049)

Abstract: This paper offers a method of realization of RGG(Range Gate Generator) with high realtime. The method is carried out in a high performance-to-price ratio FPGA chip named Spartan-3 XC3S200. Comparing with traditional methods which calculate RGG data in computer, this method transfers the task into a FPGA chip and makes sure the high accuracy, working frequence and real-time of RGG to the most extent. This paper makes the detailed discussion of the basic theory, running process and the realization of some key modules, such as serial ports and the protocol of data transmission, the realization of multiplier module, and the measure of avoiding backscatter and so on.

Key words: RGG; Spartan-3 XC3S200; realtime; SLR operating at high repetition rate