# Scalable Zero Knowledge via Cycles of Elliptic Curves

(extended version)

Eli Ben-Sasson eli@cs.technion.ac.il Technion Alessandro Chiesa alexch@mit.edu MIT

Eran Tromer tromer@cs.tau.ac.il Tel Aviv University Madars Virza madars@mit.edu MIT

## April 28, 2015

#### Abstract

Non-interactive zero-knowledge proofs of knowledge for general NP statements are a powerful cryptographic primitive, both in theory and in practical applications. Recently, much research has focused on achieving an additional property, *succinctness*, requiring the proof to be very short and easy to verify. Such proof systems are known as *zero-knowledge succinct non-interactive arguments of knowledge* (zk-SNARKs), and are desired when communication is expensive, or the verifier is computationally weak.

Existing zk-SNARK implementations have severe scalability limitations, in terms of space complexity as a function of the size of the computation being proved (e.g., running time of the NP statement's decision program). First, the size of the proving key is quasilinear in the upper bound on the computation size. Second, producing a proof requires "writing down" all intermediate values of the entire computation, and then conducting global operations such as FFTs.

The bootstrapping technique of Bitansky et al. (STOC '13), following Valiant (TCC '08), offers an approach to scalability, by recursively composing proofs: proving statements about acceptance of the proof system's own verifier (and correctness of the program's latest step). Alas, recursive composition of known zk-SNARKs has never been realized in practice, due to enormous computational cost.

Using new elliptic-curve cryptographic techniques, and methods for exploiting the proof systems' field structure and nondeterminism, we achieve the first zk-SNARK implementation that practically achieves recursive proof composition. Our zk-SNARK implementation runs random-access machine programs and produces proofs of their correct execution, on today's hardware, for any program running time. It takes constant time to generate the keys that support *all* computation sizes. Subsequently, the proving process only incurs a constant multiplicative overhead compared to the original computation's time, and an essentially-constant additive overhead in memory. Thus, our zk-SNARK implementation is the first to have a well-defined, albeit low, clock rate of "verified instructions per second".

Keywords: computationally-sound proofs, proof-carrying data, zero knowledge, elliptic curves

# Contents

| 1      | Introduction         1.1       Scalability limitations of prior zk-SNARK implementations         1.2       What we know from theory         1.3       Contributions         1.4       Summary of challenges and techniques         1.5       Roadmap | <b>3</b><br>3<br>4<br>4<br>5<br>7                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 2      | Preliminaries         2.1       Preprocessing zk-SNARKs for arithmetic circuits         2.2       Proof-carrying data         2.3       The bootstrapping approach                                                                                   | <b>7</b><br>7<br>7<br>8                                                |

| 3      | ,                                                                                                                                                                                                                                                    | <b>9</b><br>9<br>10<br>12                                              |

| 4<br>5 | <ul> <li>4.1 Intuition</li></ul>                                                                                                                                                                                                                     | 14<br>14<br>16<br>17<br>19                                             |

|        |                                                                                                                                                                                                                                                      | 19<br>20                                                               |

| 6      | <ul> <li>6.1 Specifying a machine</li></ul>                                                                                                                                                                                                          | <ul> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>27</li> </ul> |

| 7      | Evaluation on vnTinyRAM                                                                                                                                                                                                                              | 29                                                                     |

| 8      | Open problems                                                                                                                                                                                                                                        | 31                                                                     |

| Ac     | knowledgments                                                                                                                                                                                                                                        | 31                                                                     |

| A      | Computation models         A.1       Arithmetic circuits         A.2       Random-access machines         A.3       The architecture vnTinyRAM                                                                                                       | 32                                                                     |

| B      | B.1 Pairings                                                                                                                                                                                                                                         | <b>34</b><br>34<br>34                                                  |

| C      | C.1       Known constructions and security         C.2       Instantiations via elliptic curves                                                                                                                                                      | <b>36</b><br>37<br>37<br>38                                            |

| D      | Proof-carrying data for arithmetic compliance predicates                                                                                                                                                                                             | 39                                                                     |

| E      |                                                                                                                                                                                                                                                      | <b>41</b><br>42                                                        |

| Re     | ferences                                                                                                                                                                                                                                             | 43                                                                     |

# **1** Introduction

Non-interactive zero-knowledge proofs of knowledge [BFM88, NY90, BDSMP91] are a powerful tool, studied extensively both in theoretical and applied cryptography. Recently, much research has focused on achieving an additional property, *succinctness*, that requires the proof to be very short and easy to verify. A proof system with this additional property is called a *zero-knowledge Succinct Non-interactive ARgument of Knowledge* (zk-SNARK). Because succinctness is a desirable, sometimes critical, property in numerous security applications, prior work has investigated zk-SNARK implementations. Unfortunately, all implementations to date suffer from severe scalability limitations, due to high space complexity, as we now explain.

# 1.1 Scalability limitations of prior zk-SNARK implementations

**Expensive preprocessing.** As in any non-interactive zero-knowledge proof, a zk-SNARK requires a onetime trusted setup of public parameters: a *key generator* samples a proving key (used to generate proofs) and a verification key (used to check proofs); the key pair is then published as the proof system's parameters.

Most zk-SNARK constructions [Gro10, Lip12, BCIOP13, GGPR13, PGHR13, BCGTV13a, Lip13, BCTV14], including all published implementations [PGHR13, BCGTV13a, BCTV14], require *expensive preprocessing* during key generation. Namely, the key generator takes as input an upper bound on the computation size, e.g., in the form of an explicit NP decision circuit C output by a *circuit generator*; then, the key generator's space complexity, as well as the size of the output proving key, depends at least linearly on this upper bound. Essentially, the circuit C is explicitly laid out and encoded so as to produce the proof system's parameters.

One way to mitigate the costs of expensive preprocessing is to make C universal, i.e., design C so that it can handle more than one choice of program [BCTV14]. Yet, C still depends on upper bounds on the program size and number of execution steps. Moreover, even if key generation is carried out only once per circuit C, the resulting large proving key must be stored, and accessed, each time a proof is generated. Prior implementations of zk-SNARKs quickly become space-bound already for modest computation sizes, e.g., with proving keys of over 4 GB for circuits of only 16 million gates [BCTV14].<sup>1</sup>

Thus, expensive preprocessing severely limits scalability of a zk-SNARK.

**Space-intensive proof generation.** Related in part to the aforementioned expensive preprocessing, the prover in all published zk-SNARK implementations has large space complexity. Essentially, the proving process requires writing down the *entire* computation (e.g., the evaluation of the circuit C) all at once, and then conduct a global computation (such as Fast Fourier transforms, or multi-exponentiations) based on it. In particular, if C expresses the execution of a program, then proving requires writing down the full trace of intermediate states throughout the program execution.

Tradeoffs are possible, using block-wise versions of the global algorithms, and repeating the computation to reproduce segments of the trace. These decrease the prover's space complexity but significantly increase its time complexity, and thus do not adequately address scalability.

**Remark 1.1.** Even when relaxing the goal (by allowing interaction, "theorem batching", or non-zeroknowledge proofs), all published implementations of proof systems for outsourcing NP computations [SBW11, SMBW12, SVPB<sup>+</sup>12, SBVB<sup>+</sup>13, BFRS<sup>+</sup>13] also suffer from both of the above scalability limitations.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>Even worse, the reported numbers are for "data at rest": the proving key consists of a list of elliptic-curve points, which are *compressed* when not in use. However, when the prover uses the proving key to produce a proof, the points are uncompressed (and represented via projective or Jacobian coordinates), and take about three times as much space in memory.

<sup>&</sup>lt;sup>2</sup>In contrast, when outsourcing P computations, there are implementations without expensive preprocessing: [CMT12, TRMP12, Tha13] consider low-depth circuits, and [CRR11] consider outsourcing to multiple provers at least one of which is honest.

# **1.2** What we know from theory

Ideally, we would like to implement a zk-SNARK that does not suffer from either of the scalability limitations mentioned in the previous section, i.e., a zk-SNARK where:

• Key generation is *cheap* (i.e., its running time only depends on the security parameter) and *suffices for all computations* (of polynomial size). Such a zk-SNARK is called **fully succinct**.

• Proof generation is carried out *incrementally*, alongside the original computation, by updating, at each step, a proof of correctness of the computation so far. Such a zk-SNARK is called **incrementally computable**. Work in cryptography tells us that the above properties can be achieved in theoretical zk-SNARK constructions. Namely, building on the work of Valiant on incrementally-verifiable computation [Val08] and the work of Chiesa and Tromer on proof-carrying data [CT10, CT12], Bitansky et al. [BCCT13] showed how to construct zk-SNARKs that are fully-succinct and incrementally-computable.

Concretely, the approach of [BCCT13] consists of a transformation that takes as input a *preprocessing* zk-SNARK (such as one from existing implementations), and *bootstraps* it, via recursive proof composition, into a new zk-SNARK that is fully-succinct and incrementally-computable. In recursive proof composition, a prover produces a proof about an NP statement that, among other checks, also ensures the accepting computation of the proof system's own verifier. In a zk-SNARK, proof verification is asymptotically cheaper than merely verifying the corresponding NP statement; so recursive proof composition is viable, in theory. In practice, however, this step introduces concretely enormous costs: even if zk-SNARK verifiers can be executed in just a few milliseconds on a modern desktop [PGHR13, BCTV14], zk-SNARK verifiers still take millions of machine cycles to execute. Hence, known zk-SNARK implementations cannot achieve *even one step* of recursive proof composition in practical time. Thus, whether recursive proof composition can be realized in practice, with any reasonable efficiency, has so far remained an intriguing open question.

**Remark 1.2** (PCPs). Suitably instantiating Micali's "computationally-sound proofs" [Mic00] yields fullysuccinct zk-SNARKs. However, it is not known how to also achieve incremental computation with this approach (without also invoking the aforementioned approach of Bitansky et al. [BCCT13]). Indeed, [Mic00] requires probabilistically-checkable proofs (PCPs) [BFLS91], where one can achieve a prover that runs in quasilinear-time [BCGT13b], but only by requiring space-intensive computations — again due to the need to write down the entire computation and conducting global operations on it.

# 1.3 Contributions

We present the first prototype implementation that practically achieves recursive composition of zk-SNARKs. This enables us to achieve the following results:

(i) Scalable zk-SNARKs. We present the first implementation of a zk-SNARK that is fully succinct and incrementally computable. Our implementation follows the approach of Bitansky et al. [BCCT13].

Our zk-SNARK works for proving/verifying computations on a general notion of random-access machine. The key generator takes as input a *machine specification*, consisting of settings for random-access memory (number of addresses and number of bits at each address) and a CPU circuit, defining the machine's behavior. The keys sampled by the key generator support proving/verifying computations, of any polynomial length, on this machine. Thus, our zk-SNARK implementation directly supports many architectures (e.g., floating-point processors, SIMD-based processors, etc.) — one only needs to specify memory settings and a CPU circuit.

Compared to the original machine computation, our zk-SNARK only imposes a constant multiplicative overhead in time and an essentially-constant additive overhead in space. Indeed, the proving process steps through the machine's computation, each time producing a new proof that the computation is correct so far, by relying on the prior proof; each proof asserts the satisfiability of a constant-size circuit, and requires few resources in time and space to produce. Our zk-SNARK scales, on today's hardware, to any computation size.

(ii) **Proof-carrying data.** The main tool in [BCCT13]'s approach is *proof-carrying data* (PCD) [CT10, CT12], a cryptographic primitive that encapsulates the security guarantees provided by recursive proof composition. Thus, as a stepping stone towards the aforementioned zk-SNARK implementation, we also achieve the first implementation of PCD, for arithmetic circuits.

(iii) Evaluation on vnTinyRAM. We evaluate our zk-SNARK on a specific choice of random-access machine: vnTinyRAM, a simple RISC von Neumann architecture that is supported by the most recent preprocessing zk-SNARK implementation [BCTV14]. The evaluation confirms our expectations that our approach is slower for small computations but achieves scalability to large computations.

We evaluated our prototype on 16-bit and 32-bit vnTinyRAM with 16 registers (as in [BCTV14]). For instance, for 32-bit vnTinyRAM, our prototype incrementally proves correct program execution at the cost of 26.2 seconds per program step, using a 55 MB proving key and 993 MB of additional memory. In contrast, for a *T*-step program, the system of [BCTV14] requires roughly  $0.05 \cdot T$  seconds, *provided* that roughly  $3.1 \cdot T$  MB of main memory are available. Thus for T > 321 our system is more space-efficient, and the savings in space continue to grow as *T* increases. (These numbers are for an 80-bit security level.)

**The road ahead.** Obtaining scalable zk-SNARKs is but one application of PCD. More generally, PCD enables efficient "distributed theorem proving", which has applications ranging from securing the IT supply chain, to information flow control, and to distributed programming-language semantics [CT10, CT12, CTV13]. Now that a first prototype of PCD has been achieved, these applications are waiting to be explored in practice.

**Remark 1.3** (parametrization). In this work we describe a concrete implementation of a cryptographic system, whose efficiency scales with the security parameter and other quantities (e.g., wordsize of a machine, size of random-access memory, and so on). Since we make several concrete choices (e.g., fixing the security level at 80 bits, fixing vnTinyRAM's wordsize to 16 or 32 bits as in [BCTV14]) many asymptotic dependencies "collapse" to constants. We focus on scalability as a function of the computation size, i.e., the number of steps and amount of memory in the original program's execution on the concrete random-access machine.

# **1.4** Summary of challenges and techniques

As we recall in Section 2, bootstrapping zk-SNARKs involves two main ingredients: a collision-resistant hash function and a preprocessing zk-SNARK. Practical implementations of both ingredients exist. So one may conclude that "practical bootstrapping" is merely a matter of stitching together implementations of these two ingredients. As we now explain, this conclusion is mistaken, because bootstrapping a zk-SNARK in practice poses several challenges that must be tackled in order to obtain any reasonable efficiency.

**Common theme: leverage field structure.** The techniques that we employ to overcome efficiency barriers leverage the fact that the "native" NP language whose membership is proved/verified by the zk-SNARK is the satisfiability of  $\mathbb{F}$ -arithmetic circuits, for a certain finite field  $\mathbb{F}$ . While any NP statement can be reduced to  $\mathbb{F}$ -arithmetic circuits, the proof system is most efficient for statements expressible as  $\mathbb{F}$ -arithmetic circuits of small size. Prior work only partially leveraged this fact, by using circuits that conduct large-integer arithmetic or "pack" bits into field elements for non-bitwise checks (e.g., equality) [PGHR13, BCGTV13a, BFRS<sup>+</sup>13, BCTV14]. In this paper, we go further and, for improved efficiency, use circuits that conduct *field operations*.

# 1.4.1 Challenge: how to efficiently "close the loop"?

By far the most prominent challenge is efficiently "closing the loop". In the bootstrapping approach, each step requires proving a statement that (i) verifies the validity of previous zk-SNARK proofs; and (ii) checks another execution step. For recursive composition, this statement needs to be expressed as an  $\mathbb{F}$ -arithmetic circuit  $C_{pcd}$ , so that it can be proved using the very same zk-SNARK. In particular, we need to *implement the verifier V as an*  $\mathbb{F}$ -arithmetic circuit  $C_V$  (a subcircuit of  $C_{pcd}$ ).

In principle, constructing  $C_V$  is possible, because circuits are a universal model of computation. And not just in principle: much research has been devoted to improve the efficiency and functionality of circuit generators in practice [SVPB<sup>+</sup>12, BCGT13a, SBVB<sup>+</sup>13, PGHR13, BCGTV13a, BCTV14]. Hence, a reasonable approach to construct  $C_V$  is to apply a suitable circuit generator to a suitable software implementation of V.

However, such an approach is likely to be inefficient. Circuit generators strive to support complex program computations, by providing ways to efficiently handle data-dependent control flow, memory accesses, and so on. Instead, verifiers in preprocessing zk-SNARK constructions are "circuit-like" programs, consisting of few pairing-based arithmetic checks that do not use complex data-dependent control flow or memory accesses.

Thus, we want to avoid circuit generators, and somehow directly construct  $C_V$  so that its size is not huge. As we shall explain (see Section 3), this is not merely a programmatic difficulty, but there are *mathematical* obstructions to constructing  $C_V$  efficiently.

Main technique: PCD-friendly cycles of elliptic curves. In our underlying preprocessing zk-SNARK, the verifier V consists mainly of operations in an elliptic curve over a field  $\mathbb{F}'$ , and is thus expressed, most efficiently, as a  $\mathbb{F}'$ -arithmetic circuit. We observe that if this field  $\mathbb{F}'$  is the same as the aforementioned native field  $\mathbb{F}$  of the zk-SNARK's statement, then recursive composition can be orders of magnitude more efficient than otherwise. Unfortunately, as we shall explain, the "field matching"  $\mathbb{F} = \mathbb{F}'$  is mathematically impossible.

In contrast, we show how to circumvent this obstruction by using multiple, suitably-chosen elliptic curves, that lie on a *PCD-friendly cycle*. For example, a PCD-friendly 2-cycle consists of two curves such that the (prime) size of the base field of one curve equals the group order of the other curve, and vice versa. Our implementation uses a PCD-friendly cycle of elliptic curves (found at a great computational expense) to attain zk-SNARKs that are *tailored* for recursive proof composition.

Additional technique: nondeterministic verification of pairings. The zk-SNARK verifier involves, more specifically, several pairing-based checks over its elliptic curve. Yet, each pairing evaluation is very expensive, if not carefully performed. To further improve efficiency, we exploit the fact that the zk-SNARK supports NP statements, and provide a hand-optimized circuit implementation of the zk-SNARK verifier that leverages nondeterminism for improved efficiency. For instance, in our construction, we make heavy use of *affine* coordinates for both curve arithmetic and divisor evaluations [LMN10], because these are particularly efficient to *verify* (as opposed to *computing*, for which projective or Jacobian coordinates are known to be faster).

#### 1.4.2 Challenge: how to efficiently verify collision-resistant hashing?

Bootstrapping zk-SNARKs uses, at multiple places, a collision-resistant hash function H and an arithmetic circuit  $C_H$  for verifying computations of H. If not performed efficiently, this would be another bottleneck.

For instance, the aforementioned circuit  $C_{pcd}$ , besides verifying prior zk-SNARK proofs, is also tasked with verifying one step of machine execution. This involves not only checking the CPU execution but also the validity of loads and stores to random-access memory, done via memory-checking techniques based on Merkle trees [BEGKN91, BCGT13a]. Thus  $C_{pcd}$  also needs to have a subcircuit to check Merkle-tree authentication paths. Constructing such circuits is straightforward, given a circuit  $C_H$  for verifying computations of H. But the main question here is how to pick H so that  $C_H$  can be small. Indeed, if random-access memory consists of A addresses, then checking an authentication path requires at least  $\lceil \log A \rceil \cdot |C_H|$  gates. If  $C_H$  is large, this subcircuit dwarfs the CPU, and "wastes" most of the size of  $C_{pcd}$  for a single load/store.

Merely picking some standard choice of hash function H (e.g., SHA-256 or Keccak) yields  $C_H$  with tens of thousands of gates [PGHR13, BCGG<sup>+</sup>14], making hash verifications very expensive. Is this inherent?

Additional technique: field-specific hashes. We select a hash H that is tailored to efficient verification in the field  $\mathbb{F}$ . In our setting,  $\mathbb{F}$  has prime order p, so its additive group is isomorphic to  $\mathbb{Z}_p$ . Thus, a natural approach is to let H be a *modular subset-sum* function over  $\mathbb{Z}_p$ . For suitable parameter choices and for random coefficients, subset-sum functions are collision-resistant [Ajt96, GGH96]. In this paper we base all

of our collision-resistant hashing on suitable subset sums, and thereby greatly reduce the burden of hashing.<sup>3</sup>

## 1.5 Roadmap

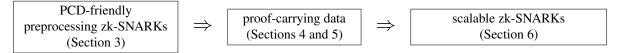

The rest of this paper is organized as follows. In Section 2 we recall the main ideas of [BCCT13]'s approach. Then we discuss our construction in more detail, in the following three steps:

In Section 7, we evaluate our system on the machine vnTinyRAM. In Section 8, we discuss open problems.

# 2 Preliminaries

We give here the essential definitions needed for the technical discussions in the body of the paper; more detailed definitions can be found in the appendices (where some definitions are taken verbatim from [BCTV14]).

We denote by  $\mathbb{F}$  a field, and by  $\mathbb{F}_n$  the field of size *n*. Throughout, we assume familiarity with finite fields; for background on these, see the book of Lidl and Niederreiter [LN97].

## 2.1 Preprocessing zk-SNARKs for arithmetic circuits

Given a field  $\mathbb{F}$ , the *circuit satisfaction problem* of an  $\mathbb{F}$ -arithmetic circuit  $C \colon \mathbb{F}^n \times \mathbb{F}^h \to \mathbb{F}^l$  is defined by the relation  $\mathcal{R}_C = \{(x, a) \in \mathbb{F}^n \times \mathbb{F}^h : C(x, a) = 0^l\}$ ; its language is  $\mathcal{L}_C = \{x \in \mathbb{F}^n : \exists a \in \mathbb{F}^h, C(x, a) = 0^l\}$ .

A **preprocessing zk-SNARK** for  $\mathbb{F}$ -arithmetic circuit satisfiability (see, e.g., [BCIOP13]) is a triple of polynomial-time algorithms (G, P, V), called *key generator*, *prover*, and *verifier*. The key generator G, given a security parameter  $\lambda$  and an  $\mathbb{F}$ -arithmetic circuit  $C : \mathbb{F}^n \times \mathbb{F}^h \to \mathbb{F}^l$ , samples a *proving key* pk and a *verification key* vk; these are the proof system's public parameters, which need to be generated only once per circuit. After that, anyone can use pk to generate non-interactive proofs for the language  $\mathcal{L}_C$ , and anyone can use the vk to check these proofs. Namely, given pk and any  $(x, a) \in \mathcal{R}_C$ , the honest prover P(pk, x, a)produces a proof  $\pi$  attesting that  $x \in \mathcal{L}_C$ ; the verifier  $V(\text{vk}, x, \pi)$  checks that  $\pi$  is a valid proof for  $x \in \mathcal{L}_C$ . A proof  $\pi$  is a proof of knowledge, as well as a (statistical) zero-knowledge proof. The succinctness property requires that  $\pi$  has length  $O_{\lambda}(1)$  and V runs in time  $O_{\lambda}(|x|)$ , where  $O_{\lambda}$  hides a (fixed) polynomial in  $\lambda$ .

See Appendix C for details.

## 2.2 Proof-carrying data

Proof-carrying data (PCD) [CT10, CT12] is a cryptographic primitive that encapsulates the security guarantees obtainable via recursive composition of proofs. Since recursive proof composition naturally involves multiple (physical or virtual) parties, PCD is phrased in the language of a dynamically-evolving *distributed computation* among mutually-untrusting computing nodes, who perform local computations, based on local data and previous messages, and then produce output messages. Given a *compliance predicate*  $\Pi$  to express local checks, the goal of PCD is to ensure that any given message *z* in the distributed computation is  $\Pi$ -compliant, i.e., is consistent with a history in which each node's local computation satisfies  $\Pi$ . This formulation includes as special cases incrementally-verifiable computation [Val08] and targeted malleability [BSW12].

Concretely, a proof-carrying data (PCD) system is a triple of polynomial-time algorithms  $(\mathbb{G}, \mathbb{P}, \mathbb{V})$ , called *key generator*, *prover*, and *verifier*. The key generator  $\mathbb{G}$  is given as input a predicate  $\Pi$  (specified as an arithmetic circuit), and outputs a proving key pk and a verification key vk; these keys allow anyone to

<sup>&</sup>lt;sup>3</sup>We note that subset-sum functions were also used in [BFRS<sup>+</sup>13], but, crucially, they were *not* tailored to the field. This is a key difference in usage and efficiency. (E.g., our hash function can be verified in  $\leq 300$  gates, while [BFRS<sup>+</sup>13] report 13,000.)

prove/verify that a piece of data z is  $\Pi$ -compliant. This is achieved by attaching a short and easy-to-verify proof to each piece of data. Namely, given pk, received messages  $\vec{z}_{in}$  with proofs  $\vec{\pi}_{in}$ , local data  $z_{loc}$ , and a claimed outgoing message z,  $\mathbb{P}$  computes a new proof  $\pi$  to attach to z, which attests that z is  $\Pi$ -compliant; the verifier  $\mathbb{V}(vk, z, \pi)$  verifies that z is  $\Pi$ -compliant. A proof  $\pi$  is a proof of knowledge, as well as a (statistical) zero-knowledge proof; succinctness requires that  $\pi$  has length  $O_{\lambda}(1)$  and  $\mathbb{V}$  runs in time  $O_{\lambda}(|z|)$ .

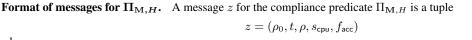

Finally, note that since  $\Pi$  is expressed as an  $\mathbb{F}$ -arithmetic circuit for a given field  $\mathbb{F}$ , the size of messages and local data are fixed; we denote these sizes by  $n_{msg}$ ,  $n_{loc} \in \mathbb{N}$ . Similarly, the number of input messages is also fixed; we call this the *arity*, and denote it by  $s \in \mathbb{N}$ . Moreover, for convenience,  $\Pi$  also takes as input a flag  $b_{base} \in \{0, 1\}$  denoting whether the node has no predecessors (i.e.,  $b_{base}$  is a "base-case" flag). Overall,  $\Pi$  takes an input  $(z, z_{loc}, \vec{z_{in}}, b_{base}) \in \mathbb{F}^{n_{msg}} \times \mathbb{F}^{n_{loc}} \times \mathbb{F}^{s \cdot n_{msg}} \times \mathbb{F}$ .

See Appendix D for details.

## 2.3 The bootstrapping approach

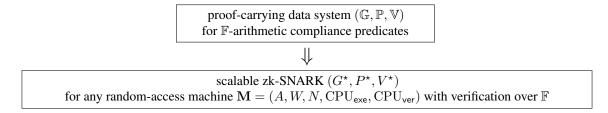

Our implementation follows [BCCT13], which we now review. The approach consists of a transformation that, on input a preprocessing zk-SNARK and a collision-resistant hash function, outputs a scalable zk-SNARK. Thus, the input zk-SNARK is *bootstrapped* into one with improved scalability properties.

So fix a preprocessing zk-SNARK (G, P, V) and collision-resistant function H. The goal is to construct a fully-succinct incrementally-computable zk-SNARK  $(G^*, P^*, V^*)$  for proving/verifying the correct execution on a given random-access machine **M**. Informally, we describe the transformation in four steps.

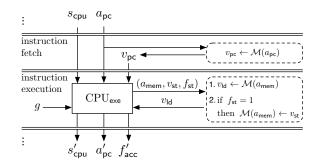

**Step 1: from zk-SNARKs to PCD.** The first step, independent of **M**, is to construct a PCD system  $(\mathbb{G}, \mathbb{P}, \mathbb{V})$ , by using the zk-SNARK (G, P, V). This step involves recursive composition of zk-SNARK proofs.

**Step 2: delegate the machine's memory.** The second step is to reduce the footprint of the machine  $\mathbf{M}$ , by delegating its random-access memory to an untrusted storage, via standard memory-checking techniques based on Merkle trees [BEGKN91, BCGT13a]. We thus modify  $\mathbf{M}$  so that its "CPU" receives values loaded from memory as nondeterministic guesses, along with corresponding authentication paths that are checked against the root of a Merkle tree based on the hash function H. Thus, the entire state of  $\mathbf{M}$  only consists of a (short) CPU state, and a (short) root of the Merkle tree that "summarizes" memory.<sup>4</sup>

Step 3: design a predicate  $\Pi_{M,H}$  for step-wise verification. The third step is to design a compliance predicate  $\Pi_{M,H}$  that ensures that the only  $\Pi_{M,H}$ -compliant messages z are the ones that result from the correct execution of the (modified) machine M, one step at a time; this is analogous to the notion of incremental computation [Val08]. Crucially, because  $\Pi_{M,H}$  is only asked to verify one step of execution at a time, we can implement  $\Pi_{M,H}$ 's requisite checks with a circuit of merely constant size.

Step 4: construct new proof system. The new zk-SNARK  $(G^*, P^*, V^*)$  is constructed as follows. The new key generator  $G^*$  is set to the PCD generator  $\mathbb{G}$  invoked on  $\Pi_{\mathbf{M},H}$ . The new prover  $P^*$  uses the PCD prover  $\mathbb{P}$  to prove correct execution of  $\mathbf{M}$ , one step at a time and conducting the incremental distributed computation "in his head". The new verifier  $V^*$  simply uses the PCD verifier  $\mathbb{V}$  to verify  $\Pi_{\mathbf{M},H}$ -compliance. In sum, since  $\Pi_{\mathbf{M},H}$  is small and suffices for all computations, the new zk-SNARK is scalable: it is fully succinct; moreover, because the new prover computes a proof for each new step based on the previous one, it is also incrementally computable. (See Appendix E for definitions of these properties.)

Our goal is to realize the above approach in a practical implementation.

**Security of recursive proof composition.** Security in [BCCT13] is proved by using the *proof-of-knowledge property* of zk-SNARKs; we refer the interested reader to [BCCT13] for details. One aspect that must be addressed from a theoretical standpoint is the *depth* of composition. Depending on assumption strength, one

<sup>&</sup>lt;sup>4</sup> Similarly to [BCCT13] and our realization thereof, Braun et al. [BFRS<sup>+</sup>13] leverage memory-checking techniques based on Merkle trees [BEGKN91] for the purpose of enabling a circuit to "securely" load from and store to an untrusted storage. However, the systems' goals (delegation of MapReduce computations via a 2-move protocol) and techniques are different (cf. Footnote 3).

may have to recursively compose proofs in "proof trees above the message chain", rather than along the chain. From a practical perspective we make the heuristic assumption that depth of composition does not affect security of the zk-SNARK, because no evidence suggests otherwise for the constructions that we use.

# **3** PCD-friendly preprocessing zk-SNARKs

We first construct preprocessing zk-SNARKs that are tailored for efficient recursive composition of proofs. Later, in Section 5, we discuss how we use such zk-SNARKs to construct a PCD system.

## 3.1 PCD-friendly cycles of elliptic curves

Let  $\mathbb{F}$  be a finite field, and (G, P, V) a preprocessing zk-SNARK for  $\mathbb{F}$ -arithmetic satisfiability. The idea of recursive proof composition is to prove/verify satisfiability of an  $\mathbb{F}$ -arithmetic circuit  $C_{pcd}$  that checks the validity of previous proofs (among other things). Thus, we need to implement the verifier V as an  $\mathbb{F}$ -arithmetic circuit  $C_V$ , to be used as a sub-circuit of  $C_{pcd}$ .

How to write  $C_V$  depends on the algorithm of V, which in turn depends on which elliptic curve is used to instantiate the pairing-based zk-SNARK. For prime r, in order to prove statements about  $\mathbb{F}_r$ -arithmetic circuit satisfiability, one instantiates (G, P, V) using an elliptic curve E defined over some finite field  $\mathbb{F}_q$ , where the group  $E(\mathbb{F}_q)$  of  $\mathbb{F}_q$ -rational points has order  $r = \#E(\mathbb{F}_q)$  (or, more generally, r divides  $\#E(\mathbb{F}_q)$ ). Then, all of V's arithmetic computations are over  $\mathbb{F}_q$ , or extensions of  $\mathbb{F}_q$  up to degree k, where k is the embedding degree of E with respect to r (i.e., the smallest integer k such that r divides  $q^k - 1$ ). (See Appendix C.2.)

We motivate our approach by first describing two "failed attempts".

Attempt #1: pick curve with q = r. Ideally, we would like to select a curve E with q = r, so that V's arithmetic is over the *same field* for which V's native NP language is defined. Unfortunately, this cannot happen: the condition that E has embedding degree k with respect to r implies that r divides  $q^k - 1$ , which implies that  $q \neq r$ . The same implication holds even if  $E(\mathbb{F}_q)$  has a non-prime order n and the prime r (with respect to which k is defined) only divides n. So, while appealing, this idea cannot even be instantiated.<sup>5</sup>

Attempt #2: long arithmetic. Since we are stuck with  $q \neq r$ , we may consider doing "long arithmetic": simulating  $\mathbb{F}_q$  operations via  $\mathbb{F}_r$  operations, by working with bit chunks to perform integer arithmetic, and modding out by q when needed. Alas, having to work at the "bit level" implies a blowup on the order of  $\log q$  compared to native arithmetic. So, while this approach can at least be instantiated, it is very expensive.<sup>6</sup>

**Our approach: cycle through multiple curves.** We formulate, and instantiate, a new property for elliptic curves that enables us to completely circumvent long arithmetic, even with  $q \neq r$ . In short, our idea is to base recursive proof composition, not on a single zk-SNARK, but on *multiple* zk-SNARKs, each instantiated on a different elliptic curve, that *jointly* satisfy a special property.

For the simplest case, suppose we have two primes  $q_{\alpha}$  and  $q_{\beta}$ , and elliptic curves  $E_{\alpha}/\mathbb{F}_{q_{\alpha}}$  and  $E_{\beta}/\mathbb{F}_{q_{\beta}}$ such that  $q_{\alpha} = \#E_{\beta}(\mathbb{F}_{q_{\beta}})$  and  $q_{\beta} = \#E_{\alpha}(\mathbb{F}_{q_{\alpha}})$ , i.e., the size of the base field of one curve equals the group order of the other curve, and vice versa. We then construct two preprocessing zk-SNARKs  $(G_{\alpha}, P_{\alpha}, V_{\alpha})$  and  $(G_{\beta}, P_{\beta}, V_{\beta})$ , respectively instantiated on the two curves  $E_{\alpha}/\mathbb{F}_{q_{\alpha}}$  and  $E_{\beta}/\mathbb{F}_{q_{\beta}}$ .

Now note that  $(G_{\alpha}, P_{\alpha}, V_{\alpha})$  works for  $\mathbb{F}_{q_{\beta}}$ -arithmetic circuit satisfiability, but all of  $V_{\alpha}$ 's arithmetic computations are over  $\mathbb{F}_{q_{\alpha}}$  (or extensions thereof); while  $(G_{\beta}, P_{\beta}, V_{\beta})$  works for  $\mathbb{F}_{q_{\alpha}}$ -arithmetic circuits, but  $V_{\beta}$ 's arithmetic computations are over  $\mathbb{F}_{q_{\beta}}$  (or extensions thereof). Instead of having each zk-SNARK handle statements about its *own* verifier, as in the prior attempts (i.e., writing  $V_{\alpha}$  as a  $\mathbb{F}_{q_{\beta}}$ -arithmetic circuit, or  $V_{\beta}$  as

<sup>&</sup>lt;sup>5</sup>Besides, the condition  $q = \#E(\mathbb{F}_q)$  is undesirable even when not ruled out (e.g., when  $k = \infty$ ): on such curves, known as *anomalous*, discrete logarithms can be computed in polynomial time via the SSSA attack [Sem98, Sma99, SA98].

<sup>&</sup>lt;sup>6</sup>Showing that it is *provably* expensive requires stronger circuit lower bounds than currently known [Raz87, Smo87, GLS09].

a  $\mathbb{F}_{q_{\alpha}}$ -arithmetic circuit), we instead let each zk-SNARK handle statements about the verifier of the *other* zk-SNARK. That is, we write  $V_{\alpha}$  as a  $\mathbb{F}_{q_{\alpha}}$ -arithmetic circuit  $C_{V_{\alpha}}$ , and  $V_{\beta}$  as a  $\mathbb{F}_{q_{\beta}}$ -arithmetic circuit  $C_{V_{\beta}}$ .

We can then perform recursive proof composition by *alternating* between the two proof systems. Roughly, one can use  $P_{\alpha}$  to prove successful verification of a proof by  $C_{V_{\beta}}$  and, conversely,  $P_{\beta}$  to prove successful verification of a proof by  $C_{V_{\alpha}}$ . Doing so in alternation ensures that fields "match up", and no long arithmetic is needed. (This sketch omits key technical details; see Section 4.)

Since  $E_{\alpha}$  and  $E_{\beta}$  facilitate constructing PCD, we say that  $(E_{\alpha}, E_{\beta})$  is a *PCD-friendly 2-cycle of elliptic curves*. More generally, the idea extends to cycling through  $\ell$  curves satisfying this definition:

**Definition 3.1.** Let  $E_0, \ldots, E_{\ell-1}$  be elliptic curves, respectively defined over finite fields  $\mathbb{F}_{q_0}, \ldots, \mathbb{F}_{q_{\ell-1}}$ , with each  $q_i$  a prime. We say that  $(E_0, \ldots, E_{\ell-1})$  is a **PCD-friendly cycle** of length  $\ell$  if each  $E_i$  is pairing friendly and, moreover,  $\forall i \in \{0, \ldots, \ell-1\}, q_i = \#E_{i+1 \mod \ell}(\mathbb{F}_{q_{i+1} \mod \ell})$ .

To our knowledge this notion has not been explicitly sought before.<sup>7</sup> Though, fortunately, a family that satisfies this notion is already known, as discussed in the next subsection.

**Remark 3.2** (relaxation). One can relax Definition 3.1 to require a weaker, but still useful, condition: for each  $i \in \{0, ..., \ell - 1\}$ ,  $q_i$  divides  $\#E(\mathbb{F}_{i+1 \mod \ell})$ . Even if weaker, this condition is *still* very strong. For instance, it implies that each curve  $E_i$  has  $\rho$ -value  $\approx 1$ , i.e., that each  $E_i$  has near-prime order.<sup>8</sup> Constructing pairing-friendly curves with such good  $\rho$ -values is challenging even without the cycle condition!

Hence, generic methods such as Cocks–Pinch [CP01] and Dupont–Enge–Morain [DEM05], which yield (with high probability) curves with  $\rho$ -values > 1 (specifically,  $\approx$  2), cannot be used to construct PCD-friendly cycles.<sup>9</sup> This also applies to generalizations of the Cocks–Pinch method [BLS03, BW05, SB06] that improve the  $\rho$ -value to be  $1 < \rho < 2$ . In this work we do not investigate the above relaxation because, we can fulfill Definition 3.1 with  $\ell = 2$ , the minimal length possible.

## **3.2** Two-cycles based on MNT curves

We construct pairs of elliptic curves,  $E_4$  and  $E_6$ , that form PCD-friendly 2-cycles ( $E_4$ ,  $E_6$ ). These are MNT curves [MNT01] of embedding degrees 4 and 6. Our construction also ensures that  $E_4$  and  $E_6$  are sufficiently 2-adic (see below), a desirable property for efficient implementations of preprocessing zk-SNARKs.

**MNT curves and the KT correspondence.** Miyaji, Nakabayashi, and Takano [MNT01] characterized prime-order elliptic curves with embedding degrees k = 3, 4, 6; such curves are now known as *MNT curves*. Given an elliptic curve E defined over a prime field  $\mathbb{F}_q$ , they gave necessary and sufficient conditions on the pair (q, t), where t is the *trace* of E over  $\mathbb{F}_q$ , for E to have embedding degree k = 3, 4, 6. We refer to an MNT curve with embedding degree k as an MNTk curve. Karabina and Teske [KT08] proved an explicit 1-to-1 correspondence between MNT4 and MNT6 curves:

**Theorem 3.3** ([KT08]). Let r, q > 64 be primes. Then the following two conditions are equivalent: 1. r and q represent an elliptic curve  $E_4/\mathbb{F}_q$  with embedding degree k = 4 and  $r = \#E(\mathbb{F}_q)$ ;

<sup>2.</sup> *r* and *q* represent an elliptic curve  $E_6/\mathbb{F}_r$  with embedding degree k = 6 and  $q = \#E(\mathbb{F}_r)$ .

<sup>&</sup>lt;sup>7</sup>Definition 3.1 is reminiscent, but different from, the notion of an *aliquot cycle* of elliptic curves by Silverman and Stange [SS11]. An aliquot cycle considers a *single* curve (over  $\mathbb{O}$ ) reduced at  $\ell$  primes, rather than  $\ell$  curves, and does not require pairing-friendliness.

<sup>&</sup>lt;sup>8</sup>For each  $i \in \{0, \ldots, \ell-1\}$ , the condition that  $q_{i-1}$  divides  $\#E(\mathbb{F}_i)$  implies, via the Hasse bound, that  $h_i q_{i-1} \leq q_i \cdot (1+2/\sqrt{q_i})$  for some cofactor  $h_i \in \mathbb{N}$ ; hence  $\log q_{i-1} \leq \log q_i + \log(1+2/\sqrt{q_i}) - \log h_i$ , and thus  $\frac{\log q_{i-1}}{\log q_i} \leq 1 + \frac{\log(1+2/\sqrt{q_i})}{\log q_i} \leq 1 + \frac{2}{\sqrt{q_i}\log q_i}$ . Note that each  $a_i$  is exponentially small. Therefore, for each  $i \in \{0, \ldots, \ell-1\}$ , we can upper bound the  $\rho$ -value of  $E_i$ , equal to  $\frac{\log q_i}{\log q_{i-1}}$ , as follows:  $\frac{\log q_i}{\log q_{i-1}} = \prod_{j \neq i} \frac{\log q_j - 1}{\log q_j} \leq \prod_{j \neq i} (1+a_j) = 1 + \sum_{j \neq i} a_j + \prod_{j \neq i} a_j$ . In sum, the  $\rho$ -value of  $E_i$  is upper bounded by  $1 + \epsilon_i$ , where the quantity  $\epsilon_i := \sum_{j \neq i} a_j + \prod_{j \neq i} a_j$  is exponentially small.

<sup>&</sup>lt;sup>9</sup>At best, such methods can be used to construct PCD-friendly "chains", which can be used to reduce the space complexity of preprocessing zk-SNARKs via a limited application of recursive proof composition. But the large  $\rho$ -values would imply that each recursive composition roughly doubles the cost of the zk-SNARK so that long chains do not seem to be advantageous.

#### PCD-friendly 2-cycles on MNT curves. The above theorem implies that:

Each MNT6 curve lies on a PCD-friendly 2-cycle with the corresponding MNT4 curve (and vice versa).

Thus, a PCD-friendly 2-cycle can be obtained by constructing an MNT4 curve and its corresponding MNT6 curve. Next, we explain at high level how this can be done.

**Constructing PCD-friendly 2-cycles.** First, we recall the only known method to construct MNTk curves [MNT01]. It consists of two steps:

- Step I: *curve discovery*. Find suitable  $(q, t) \in \mathbb{N}^2$  such that there exists an ordinary elliptic curve  $E/\mathbb{F}_q$  of prime order r := q + 1 t and embedding degree k.

- Step II: curve construction. Starting from (q, t), use the Complex-Multiplication method (CM method) [AM93] to compute the equation of E over  $\mathbb{F}_q$ .

The complexity of Step II depends on the *discriminant* D of E, which is the square-free part of  $4q - t^2$ . At present, the CM method is feasible for discriminants D up to size  $10^{16}$  [Sut12]. Thus, Step I is conducted in a way that results in candidate parameters (q, t) inducing relatively-small discriminants, to aid Step II. (Instead, "most" (q, t) induce a discriminant D of size  $\sqrt{q}$ , which is too large to handle.) Concretely, [MNT01] derived, for  $k \in \{3, 4, 6\}$  and discriminant D, Pell-type equations whose solutions yield candidate parameters (q, t)for MNTk curves  $E/\mathbb{F}_q$  of trace t and discriminant D. So Step I can be performed by iteratively solving the *MNT*k Pell-type equation, for increasing discriminant size, until a suitable (q, t) is found.

The above strategy can be extended, in a straightforward way, to construct PCD-friendly 2-cycles. First perform Step I to obtain suitable parameters  $(q_4, t_4)$  for an MNT4 curve  $E_4/\mathbb{F}_{q_4}$ ; the parameters  $(q_6, t_6)$  for the corresponding MNT6 curve  $E_6/\mathbb{F}_{q_6}$  are  $q_6 := q_4 + 1 - t_4$  and  $t_6 := 2 - t_4$ . Then perform Step II for  $(q_4, t_4)$  to compute the equation of  $E_4$ , and then also for  $(q_6, t_6)$  to compute that of  $E_6$ . The complexity in both cases is the same: one can verify that  $E_4$  and  $E_6$  have the same discriminant. The two curves  $E_4$  and  $E_6$ form a PCD-friendly 2-cycle  $(E_4, E_6)$ .

Suitable cycle parameters. We now explain what "suitable  $(q_4, t_4)$ " means in our context, by specifying a list of additional properties that we wish a PCD-friendly cycle to satisfy.

- Bit lengths. In a 2-cycle  $(E_4, E_6)$ , the curve  $E_4$  is "less secure" than  $E_6$ , because  $E_4$  has embedding degree 4 while  $E_6$  has embedding degree 6. Thus, we use  $E_4$  to set lower bounds on bit lengths. Since we aim at a security level of 80 bits, we need  $r_4 \ge 2^{160}$  and  $q_4 \ge 2^{240}$  (so that  $\sqrt{r_4} \ge 2^{80}$  and  $q_4^4 \ge 2^{960}$  [FST10]). Since  $\log r_4 \approx \log q_4$  for MNT4 curves, we only need to ensure that  $q_4$  has at least 240 bits.<sup>10</sup>

- Towering friendliness. We restrict our focus to moduli  $q_4$  and  $q_6$  that are towering friendly (i.e., congruent to 1 modulo 6) [BS10]; this improves the efficiency of arithmetic in  $\mathbb{F}_{q_4}^4$  and  $\mathbb{F}_{q_6}^6$  (and their subfields).

- 2-adicity. As discussed in [BCGTV13a, BCTV14], if a pairing-based preprocessing zk-SNARK (G, P, V) is instantiated with an elliptic curve E/𝔽<sub>q</sub> of prime order r (or with #E(𝔽<sub>q</sub>) divisible by a prime r), it is important, for efficiency reasons, that r − 1 is divisible by a large power of 2, i.e., ν<sub>2</sub>(r − 1) is large. (Recall that ν<sub>2</sub>(n), the 2-adic order of n, is the largest power of 2 dividing n.) Concretely, if G is invoked on an 𝔽<sub>r</sub>-arithmetic circuit C, it is important that ν<sub>2</sub>(r − 1) ≥ ⌈log |C|⌉. We call ν<sub>2</sub>(r − 1) the 2-adic order of E, or the 2-adicity of E. (See Appendix C.2 for more details.)

So let  $\ell_4$  and  $\ell_6$  be the target values for  $\nu_2(r_4 - 1)$  and  $\nu_2(r_6 - 1)$ . One can verify that, for any MNTbased PCD-friendly 2-cycle  $(E_4, E_6)$ , it holds that  $\nu_2(r_4 - 1) = 2 \cdot \nu_2(r_6 - 1)$ ; in other words,  $E_4$ is always "twice as 2-adic" as  $E_6$ . Thus, to achieve the target 2-adic orders, it suffices to ensure that  $\nu_2(r_4 - 1) \ge \max\{\ell_4, 2\ell_6\}$  (where, as before,  $r_4 := q_4 + 1 - t_4$ ). As we shall see (in Section 5), in this paper it will suffice to take  $\nu_2(r_4 - 1) \ge 34$ .

<sup>&</sup>lt;sup>10</sup>Alas, since  $E_4$  has a low embedding degree, the ECDLP in  $E(\mathbb{F}_{q_4})$  and DLP in  $\mathbb{F}_{q_4}^4$  are "unbalanced": the former provides 120 bits of security, while the latter only 80. Moreover, the same is true for  $E_6$ : the ECDLP in  $E(\mathbb{F}_{q_6})$  provides 120 bits of security, while the DLP in  $\mathbb{F}_{q_4}^6$  only 80. Finding PCD-friendly cycles without these inefficiencies is an open problem (see Section 8).

Of the above properties, the most restrictive one is 2-adicity, because it requires seeing enough curves until, "by sheer statistics", one finds  $(q_4, t_4)$  with a high-enough value for  $\nu_2(r_4 - 1)$ . Collecting enough samples is costly because, as discriminant size increases, the density of MNT curves decreases: empirically, one finds that the number MNT curves with discriminant  $D \leq N$  is (approximately) less than  $\sqrt{N}$  [KT08].

**An extensive computation for a suitable cycle.** Overall, finding and constructing a suitable cycle required a substantial computational effort.

- Cycle discovery. In order to find suitable parameters for a cycle, we explored a large space: all discriminants up to 1.1 · 10<sup>15</sup>, requiring about 610,000 core-hours on a large cluster of modern x86 servers. Our search algorithm is a modification of [KT08, Algorithm 3]. Among all the 2-cycles that we found, we selected parameters (q<sub>4</sub>, t<sub>4</sub>) and (q<sub>6</sub>, t<sub>6</sub>) for a 2-cycle (E<sub>4</sub>, E<sub>6</sub>) of curves such that: (i) q<sub>4</sub>, q<sub>6</sub> each have 298 bits; (ii) q<sub>4</sub>, q<sub>6</sub> are towering friendly; and (iii) ν<sub>2</sub>(r<sub>4</sub> 1) = 34 and ν<sub>2</sub>(r<sub>6</sub> 1) = 17. The bit length of q<sub>4</sub>, q<sub>6</sub> is higher than the lower bound of 240; we entail this cost so to pick a rare cycle with high 2-adicity, which helps the zk-SNARK's efficiency more than the slowdown incurred by the higher bit length.

- *Cycle construction*. Both  $E_4$  and  $E_6$  have discriminant 614144978799019, whose size requires state-of-the-art techniques in the CM method [Sut11, ES10, Sut12] in order to explicitly construct the curves.<sup>11</sup>

Below, we report the parameters and equations for the 2-cycle  $(E_4, E_6)$  that we selected.

$$\begin{split} &E_4/\mathbb{F}_{q_4}: y^2 = x^3 + A_4x + B_4 \text{ where} \\ &A_4 = 2, \\ &B_4 = 423894536526684178289416011533888240029318103673896002803341544124054745019340795360841685, \\ &q_4 = 475922286169261325753349249653048451545124879242694725395555128576210262817955800483758081. \\ &E_6/\mathbb{F}_{q_6}: y^2 = x^3 + A_6x + B_6 \text{ where} \\ &A_6 = 11, \\ &B_6 = 106700080510851735677967319632585352256454251201367587890185989362936000262606668469523074, \\ &q_6 = 475922286169261325753349249653048451545124878552823515553267735739164647307408490559963137. \end{split}$$

**Security.** One may wonder if curves lying on PCD-friendly cycles are weak (e.g., in terms of DL hardness). Yet, MNT4 and MNT6 curves of suitable parameters are widely believed to be secure, and they *all* fall in PCD-friendly 2-cycles. The additional requirement of high 2-adicity is not known to cause weakness either.

## 3.3 A matched pair of preprocessing zk-SNARKs

Based on the PCD-friendly cycle  $(E_4, E_6)$ , we designed and constructed two preprocessing zk-SNARKs for arithmetic circuit satisfiability:  $(G_4, P_4, V_4)$  based on the curve  $E_4$ , and  $(G_6, P_6, V_6)$  on  $E_6$ . The software implementation follows [BCTV14], the fastest preprocessing zk-SNARK implementation for circuits at the time of writing. We thus adapt the techniques in [BCTV14] to our algebraic setting, which consists of the two MNT curves  $E_4$  and  $E_6$ , and achieve efficient implementations of  $(G_4, P_4, V_4)$  and  $(G_6, P_6, V_6)$ .

The implementation itself entails many algorithmic and engineering details, and we refer the reader to [BCTV14] for a discussion of these techniques. We only provide a high-level efficiency comparison between the preprocessing zk-SNARK of [BCTV14] based on Edwards curves (also at 80-bit security), and our implementations of  $(G_4, P_4, V_4)$  and  $(G_6, P_6, V_6)$ ; see Figure 1. Our implementation is slower, because of two main reasons: (i) MNT curves do not enjoy advantageous properties that Edwards curves do; and (ii) the modulus sizes are larger (298 bits in our case vs. 180 bits in [BCTV14]). On the other hand, the fact that MNT curves lie on a PCD-friendly 2-cycle is crucial for the PCD construction described next.

<sup>&</sup>lt;sup>11</sup>The authors are grateful to Andrew V. Sutherland for generous help in running the CM method on such a large discriminant.

|               | 80 bits of security                                            |        |                 |  |

|---------------|----------------------------------------------------------------|--------|-----------------|--|

|               | $(G_{Ed}, P_{Ed}, V_{Ed})$ $(G_4, P_4, V_4)$ $(G_6, P_6, V_6)$ |        |                 |  |

| Key generator | 12.4 s                                                         | 33.9 s | 48.8 s          |  |

| Prover        | 13.0 s                                                         | 36.5 s | 49.4 s          |  |

| Verifier      | 4.4 ms                                                         | 9.1 ms | 16.7 ms         |  |

| Proof size    | 230 B                                                          | 337 B  | $374\mathrm{B}$ |  |

Figure 1: Comparison of  $(G_{Ed}, P_{Ed}, V_{Ed})$ ,  $(G_4, P_4, V_4)$ , and  $(G_6, P_6, V_6)$ , on a circuit C with  $2^{17}$  gates and inputs of 10 field elements. The size of C was chosen so that the 2-adicity of each zk-SNARK's curve is high enough (i.e.,  $\nu_2(r_i - 1) \ge 17$  for i = Ed, 4, 6). The experiment was conducted on our benchmarking machine (described in Section 7), running in single-thread mode. (The reported times are the average of 10 experiments, with standard deviation less than 1%.)

# 4 Proof-carrying data from PCD-friendly zk-SNARKs

In Section 3 we formulated, and instantiated, PCD-friendly cycles of elliptic curves (see Definition 3.1); this notion was motivated by efficiency considerations arising when recursively composing zk-SNARK proofs. Roughly, given two zk-SNARKs based on elliptic curves forming a PCD-friendly 2-cycle, one can alternate between the two proof systems, and the 2-cycle property ensures that fields "match up" at each recursive verification, allowing for an efficient circuit implementation of the verifier of both proof systems.

The discussion so far, however, is only a sketch of the approach and omits key technical details. We now spell out these by describing how to construct a PCD system, given the two zk-SNARKs. So let  $(E_{\alpha}, E_{\beta})$  be a PCD-friendly 2-cycle of elliptic curves, and let  $(G_{\alpha}, P_{\alpha}, V_{\alpha})$  and  $(G_{\beta}, P_{\beta}, V_{\beta})$  be two preprocessing zk-SNARKs respectively instantiated with the two elliptic curves  $E_{\alpha}/\mathbb{F}_{q_{\alpha}}$  and  $E_{\beta}/\mathbb{F}_{q_{\beta}}$ . Note that:

•  $(G_{\alpha}, P_{\alpha}, V_{\alpha})$  works for  $\mathbb{F}_{r_{\alpha}}$ -arithmetic circuit satisfiability, while  $V_{\alpha}$ 's computations are over  $\mathbb{F}_{q_{\alpha}}$ ; and

•  $(G_{\beta}, P_{\beta}, V_{\beta})$  works for  $\mathbb{F}_{r_{\beta}}$ -arithmetic circuit satisfiability, while  $V_{\beta}$ 's computations are over  $\mathbb{F}_{q_{\beta}}$ .

Due to the 2-cycle property,  $\mathbb{F}_{r_{\alpha}}$  equals  $\mathbb{F}_{q_{\beta}}$ , and  $\mathbb{F}_{r_{\beta}}$  equals  $\mathbb{F}_{q_{\alpha}}$ . Our goal is to use  $(G_{\alpha}, P_{\alpha}, V_{\alpha})$  and  $(G_{\beta}, P_{\beta}, V_{\beta})$ , along with other ingredients, to construct a PCD system  $(\mathbb{G}, \mathbb{P}, \mathbb{V})$ .

**Remark 4.1** (longer cycles). As we have PCD-friendly cycles of length  $\ell = 2$ , the PCD construction described in this section (including our code) is specialized to this case. One can extend the construction to work with (preprocessing zk-SNARKs based on) PCD-friendly cycles of length  $\ell > 2$ .

## 4.1 Intuition

We begin by giving the intuition behind our construction of the PCD generator  $\mathbb{G}$ , prover  $\mathbb{P}$ , and verifier  $\mathbb{V}$ . For simplicity, for now, we focus on the case where each node receives a single input message (i.e., the special case of "message chains" having arity s = 1).

**Starting point.** A natural first attempt is to construct two arithmetic circuits,  $C_{pcd,\alpha}$  over  $\mathbb{F}_{r_{\alpha}}$  and  $C_{pcd,\beta}$  over  $\mathbb{F}_{r_{\beta}}$ , that, for a given compliance predicate  $\Pi$ , work as follows.

| $C_{pcd,lpha}(x,a)$                                                                      | $  C_{pcd,eta}(x,a)$                                                                       |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 1. Parse the input x as $(vk_{\alpha}, vk_{\beta}, z)$ .                                 | 1. Parse the input x as $(vk_{\alpha}, vk_{\beta}, z)$ .                                   |

| 2. Parse the witness a as $(z_{loc}, z_{in}, \pi_{in})$ .                                | 2. Parse the witness a as $(z_{loc}, z_{in}, \pi_{in})$ .                                  |

| 3. If $\pi_{in} = 0$ (base case), set $b_{base} := 1$ .                                  | 3. If $\pi_{in} = 0$ (base case), set $b_{base} := 1$ .                                    |

| 4. If $\pi_{in} \neq 0$ (not base case), set $b_{base} := 0$ and                         | 4. If $\pi_{in} \neq 0$ (not base case), set $b_{base} := 0$ and                           |

| check that $V_{\beta}(vk_{\beta}, (vk_{\alpha}, vk_{\beta}, z_{in}), \pi_{in})$ accepts. | check that $V_{\alpha}(vk_{\alpha}, (vk_{\alpha}, vk_{\beta}, z_{in}), \pi_{in})$ accepts. |

| 5. Check that $\Pi(z, z_{\text{loc}}, z_{\text{in}}, b_{\text{base}}) = 0.$              | 5. Check that $\Pi(z, z_{\text{loc}}, z_{\text{in}}, b_{\text{base}}) = 0.$                |

|                                                                                          |                                                                                            |

In other words,  $C_{pcd,\alpha}$  checks  $\Pi$ -compliance at a node and also verifies a previous proof, relative to  $V_{\beta}$ ; while  $C_{pcd,\beta}$  does the same, but verifies a previous proof relative to  $V_{\alpha}$ . Also note that the input x, but not the witness a (over which we have no control), specifies the choice of verification keys.

More precisely, on input II, the PCD generator  $\mathbb{G}$  would work as follows: (i) construct  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$  from II; (ii) sample two key pairs,  $(pk_{\alpha}, vk_{\alpha}) \leftarrow G_4(C_{pcd,\alpha})$  and  $(pk_{\beta}, vk_{\beta}) \leftarrow G_6(C_{pcd,\beta})$ ; and (iii) output  $pk := (pk_{\alpha}, pk_{\beta}, vk_{\alpha}, vk_{\beta})$  and  $vk := (vk_{\alpha}, vk_{\beta})$ . On input proving key pk, outgoing message z, local data  $z_{loc}$ , and incoming message  $z_{in}$ , the PCD prover  $\mathbb{P}$  would invoke  $P_{\alpha}(pk_{\alpha}, x, a)$  if  $\pi_{in}$  is relative to  $V_{\beta}$  or  $P_{\beta}(pk_{\beta}, x, a)$  if  $\pi_{in}$  is relative to  $V_{\alpha}$ , where  $x := (vk_{\alpha}, vk_{\beta}, z)$  and  $a := (z_{loc}, z_{in}, \pi_{in})$ . Finally, on input verification key vk, message z, and proof  $\pi$ , the PCD verifier  $\mathbb{V}$  would either invoke  $V_{\alpha}(vk_{\alpha}, x, \pi)$  or  $V_{\beta}(vk_{\beta}, x, \pi)$ , where  $x := (vk_{\alpha}, vk_{\beta}, z)$ .

However, the above simple sketch suffers from two main problems, which we now describe.

**Problem #1.** The compliance predicate  $\Pi$  is an arithmetic circuit. However, should  $\Pi$  be defined over  $\mathbb{F}_{r_{\alpha}}$  or  $\mathbb{F}_{r_{\beta}}$ ? If  $\Pi$  is defined over  $\mathbb{F}_{r_{\alpha}}$ , then the  $\mathbb{F}_{r_{\beta}}$ -arithmetic circuit  $C_{\mathsf{pcd},\beta}$  will be very inefficient, because it has to evaluate  $\Pi$  over the "wrong" field; conversely, if  $\Pi$  is defined over  $\mathbb{F}_{r_{\beta}}$ , then  $C_{\mathsf{pcd},\alpha}$  will be very inefficient.

**Problem #2.** In known preprocessing zk-SNARK constructions, including the one underlying  $(G_{\alpha}, P_{\alpha}, V_{\alpha})$  and  $(G_{\beta}, P_{\beta}, V_{\beta})$ , a verification key has length  $\ell(n) > n$ , where n is the size of the input to the circuit with respect to which the key was created. Thus, it is not possible to obtain either vk<sub> $\alpha$ </sub> or vk<sub> $\beta$ </sub> that works for inputs of the form  $x = (vk_{\alpha}, vk_{\beta}, z)$ .

**Our solution (at high level).** To address the first problem, we simply "pick one side": only one of  $C_{pcd,\alpha}$ and  $C_{pcd,\beta}$  evaluates  $\Pi$ , while the other circuit merely enables the PCD prover to translate a proof relative to one zk-SNARK verifier to one relative to the other zk-SNARK verifier. Arbitrarily, we pick  $C_{pcd,\alpha}$  to be the one that evaluates  $\Pi$ ; in particular,  $\Pi$  will be an  $\mathbb{F}_{r_{\alpha}}$ -arithmetic circuit.<sup>12</sup> (The choice of  $C_{pcd,\alpha}$  is without loss of generality, since we can always relabel: if  $(E_{\alpha}, E_{\beta})$  is PCD-friendly 2-cycle, so is  $(E_{\beta}, E_{\alpha})$ .)

To address the second problem, the ideal solution is to simply hardcode  $vk_{\beta}$  in  $C_{pcd,\alpha}$  and  $vk_{\alpha}$  in  $C_{pcd,\beta}$ (and let an input x consist only of a message z). However, this is not possible:  $vk_{\beta}$  depends on  $C_{pcd,\beta}$ , while  $vk_{\alpha}$  depends on  $C_{pcd,\alpha}$  (i.e., there is a circular dependency). We thus proceed as follows. We hardcode  $vk_{\alpha}$  in  $C_{pcd,\beta}$ . Then, for  $vk_{\beta}$ , we rely on collision-resistant hashing. Namely, inputs x have the form  $(\chi_{\beta}, z)$  where, allegedly,  $\chi_{\beta}$  is the hash of  $vk_{\beta}$ . We modify  $C_{pcd,\alpha}$  to check that this holds:  $C_{pcd,\alpha}$ 's witness is extended to (allegedly) contain  $vk_{\beta}$  and then  $C_{pcd,\alpha}$  checks that  $H_{\alpha}(vk_{\beta}) = \chi_{\beta}$ , where  $H_{\alpha}: \{0,1\}^{m_{H,\alpha}} \to \mathbb{F}_{r_{\alpha}}^{d_{H,\alpha}}$  is a suitable collision-resistant hash function.

The above modifications to  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$  yield the following construction.

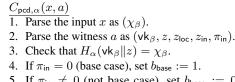

C<sub>pcd,α</sub>(x, a)

Parse the input x as (χ<sub>β</sub>, z).

Parse the witness a as (vk<sub>β</sub>, z<sub>loc</sub>, z<sub>in</sub>, π<sub>in</sub>).

Check that H<sub>α</sub>(vk<sub>β</sub>) = χ<sub>β</sub>.

If π<sub>in</sub> = 0 (base case), set b<sub>base</sub> := 1.

If π<sub>in</sub> ≠ 0 (not base case), set b<sub>base</sub> := 0 and check that V<sub>β</sub>(vk<sub>β</sub>, (χ<sub>β</sub>, z<sub>in</sub>), π<sub>in</sub>) accepts.

Check that Π(z, z<sub>loc</sub>, z<sub>in</sub>, b<sub>base</sub>) = 0.

$\begin{array}{l} \frac{C_{\mathsf{pcd},\beta}(x,a)}{1. \ \mathsf{Parse the input } x \ \mathrm{as} \ (\chi_{\beta},z). \\ 2. \ \mathsf{Parse the witness} \ a \ \mathrm{as} \ (\pi_{\alpha}). \\ 3. \ \mathsf{Check that} \ V_{\alpha} \big(\mathsf{vk}_{\alpha}, (\chi_{\beta},z), \pi_{\alpha}\big) \ \mathrm{accepts.} \end{array}$

Unfortunately, while the above two fixes make  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$  well-defined, the use of hashing makes  $C_{pcd,\alpha}$  large, as we now explain. The verification key vk<sub>\beta</sub> consists of various points on the elliptic curve  $E_{\beta}/\mathbb{F}_{q_{\beta}}$  (or a twist of it). Recalling that  $\mathbb{F}_{q_{\beta}}$  equals  $\mathbb{F}_{r_{\alpha}}$  (the field of definition of  $C_{pcd,\alpha}$ ), we represent vk<sub>\beta</sub> as a list of elements of  $\mathbb{F}_{q_{\beta}}$ , because the (circuit implementing the) verifier  $V_{\beta}$  uses vk<sub>\beta</sub> for computations in  $\mathbb{F}_{q_{\beta}}$ . Unfortunately,  $H_{\alpha}$  only accepts binary strings as input, and the translation from vk<sub>\beta</sub> to its binary representation incurs a log  $q_{\beta}$  blow up — a nontrivial cost. We do not know how to eliminate this cost.<sup>13</sup>

Thus, instead, we further modify  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$  so to shorten  $vk_{\beta}$ . Indeed, if  $C_{pcd,\beta}$  accepts inputs of *n* elements in  $\mathbb{F}_{r_{\beta}}$ , then  $vk_{\beta}$  consists of  $\ell_{vk,\beta}(n)$  elements in  $\mathbb{F}_{q_{\beta}}$ ; hence, we seek to reduce *n*. To do so, instead of working with messages of the form  $x = (\chi_{\beta}, z)$ , we work with messages of the form  $x = (\chi_{\beta})$ , by also hashing *z* along with  $vk_{\beta}$  (both of which are now supplied in the witness), as follows.

- 5. If  $\pi_{in} \neq 0$  (not base case), set  $b_{base} := 0$  and check that  $V_{\beta}(\mathsf{vk}_{\beta}, H_{\alpha}(\mathsf{vk}_{\beta} || z_{in}), \pi_{in})$  accepts.

- 6. Check that  $\Pi(z, z_{\text{loc}}, z_{\text{in}}, b_{\text{base}}) = 0.$

$C_{\mathsf{pcd},\beta}(x,a)$

- 1. Parse the input x as  $(\chi_{\beta})$ .

- 2. Parse the witness a as a zk-SNARK proof  $\pi_{\alpha}$ .

- 3. Check that  $V_{\alpha}(\mathsf{vk}_{\alpha}, \chi_{\beta}, \pi_{\alpha})$  accepts.

<sup>&</sup>lt;sup>12</sup>Alternatively, we could restrict  $\Pi$  to be a boolean circuit, so that it can be easily evaluated by  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$ . But this foregoes  $\Pi$ 's ability to conduct field operations in large prime fields. Thus, it is more efficient to "give up" on  $C_{pcd,\beta}$ , and only let  $C_{pcd,\alpha}$  evaluate  $\Pi$ , and retain the expressive power of arithmetic circuits. (Other alternatives are possible, but we do not explore them.)

<sup>&</sup>lt;sup>13</sup>As explained in Section 5.2, we are not aware of a collision-resistant hash function  $H_{\alpha}$ , which can be easily verified over  $\mathbb{F}_{r_{\alpha}}$ , that accepts inputs represented as strings of elements in  $\mathbb{F}_{r_{\alpha}}$ . So, we are "stuck" with binary inputs.

**Further details.** The above discussion omits various technical details and optimizations.

For instance, thus far we have ignored the fact that, while  $C_{pcd,\alpha}$  expects inputs over  $\mathbb{F}_{r_{\alpha}}$ ,  $C_{pcd,\beta}$  expects inputs over  $\mathbb{F}_{r_{\beta}}$ . Since  $x = \chi_{\beta}$  lies in  $\mathbb{F}_{r_{\alpha}}^{d_{H,\alpha}}$  (as it is the output of  $H_{\alpha}$ ), we cannot use the same representation of it for both  $C_{\mathsf{pcd},\alpha}$  and  $C_{\mathsf{pcd},\beta}$ ; instead, we need two representations:  $x_{\alpha} \in \mathbb{F}_{r_{\alpha}}^{n_{\alpha}}$  for  $C_{\mathsf{pcd},\alpha}$ , and  $x_{\beta} \in \mathbb{F}_{r_{\beta}}^{n_{\beta}}$ for  $C_{\mathsf{pcd},\beta}$ . Naturally, for the first, we can set  $n_{\alpha} := d_{H,\alpha}$ , and let  $x_{\alpha} := \chi_{\beta}$ . For the second, merely letting  $x_{\beta}$  be the list of  $n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil$  bits in  $\chi_{\beta}$  is *not* efficient: it would cause vk<sub>\beta</sub> to have length  $\ell_{vk,\beta}(n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil)$ . Instead, we let  $x_{\beta}$  store these bits into as few elements of  $\mathbb{F}_{r_{\beta}}$  as possible; specifically,  $n_{\beta} := \lceil \frac{n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil}{\lceil \log r_{\beta} \rceil} \rceil$  of them. So let:

•  $S_{\alpha \to \beta} \colon \mathbb{F}_{r_{\alpha}}^{n_{\alpha}} \to \mathbb{F}_{r_{\alpha}}^{n_{\beta} \cdot \lceil \log r_{\beta} \rceil}$  denote the function that maps  $x_{\alpha}$  to (the binary representation of)  $x_{\beta}$ ; and •  $S_{\alpha \leftarrow \beta} \colon \mathbb{F}_{r_{\beta}}^{n_{\beta}} \to \mathbb{F}_{r_{\beta}}^{n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil}$  denote the function that maps  $x_{\beta}$  back to (the binary representation of)  $x_{\alpha}$ .

The above implies that we need to further modify  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$ , and include explicit subcircuits  $C_{S,\alpha\to\beta}$ and  $C_{S,\alpha \leftarrow \beta}$  to carry out these "type conversions"; both of these circuits are simple to construct, and have size  $|C_{S,\alpha \to \beta}| = |C_{S,\alpha \leftarrow \beta}| = n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil$ .

Moreover, we leverage precomputation techniques [BCTV14]. A zk-SNARK verifier V can be viewed as two functions: an "offline" function  $V^{\text{offline}}$  that, given the verification key vk, computes a *processed verification key* pvk; and an "online" function  $V^{\text{online}}$  that, given pvk, an input x, and proof  $\pi$ , computes the decision bit. (I.e.,  $V(\mathsf{vk}, x, \pi) := V^{\text{online}}(V^{\text{offline}}(\mathsf{vk}), x, \pi)$ .) Precomputation offers a tradeoff: while  $V^{\text{online}}$ is cheaper to compute than V, pvk is larger than vk (in each case, the difference is an additive constant). In our setting, it turns out that it pays off to use precomputation techniques only in  $C_{pcd,\beta}$  but not in  $C_{pcd,\alpha}$ .

We address all the details in the next subsection, where we give the construction of the PCD system.

#### 4.2 Construction

We now describe in more detail our construction of the PCD generator  $\mathbb{G}$ , prover  $\mathbb{P}$ , and verifier  $\mathbb{V}$ . Throughout, we fix a message size  $n_{msg} \in \mathbb{N}$ , local-data size  $n_{loc} \in \mathbb{N}$ , and arity  $s \in \mathbb{N}$ . The construction will then work for  $\mathbb{F}_{r_{\alpha}}$ -arithmetic compliance predicates  $\Pi \colon \mathbb{F}_{r_{\alpha}}^{n_{\text{msg}}} \times \mathbb{F}_{r_{\alpha}}^{n_{\text{loc}}} \times \mathbb{F}_{r_{\alpha}}^{s \cdot n_{\text{msg}}} \times \mathbb{F}_{r_{\alpha}} \to \mathbb{F}_{r_{\alpha}}^{l}$  (i.e., for message size  $n_{\text{msg}}$ , local-data size  $n_{\text{loc}}$ , arity s, and some output size  $l \in \mathbb{N}$ ). In terms of ingredients, we make use of the following arithmetic circuits:

- An  $\mathbb{F}_{r_{\alpha}}$ -arithmetic circuit  $C_{H,\alpha}$ , implementing a collision-resistant function  $H_{\alpha}: \{0,1\}^{m_{H,\alpha}} \to \mathbb{F}_{r_{\alpha}}^{d_{H,\alpha}}$  such that  $m_{H,\alpha} \ge \left(\ell_{\mathsf{vk},\beta}(n_{\beta}) + n_{\mathsf{msg}}\right) \cdot \lceil \log r_{\alpha} \rceil$ , where  $n_{\alpha} := d_{H,\alpha}$  and  $n_{\beta} := \lceil \frac{n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil}{\lfloor \log r_{\beta} \rceil} \rceil$ .

- An F<sub>r<sub>α</sub></sub>-arithmetic circuit C<sub>S,α→β</sub>, implementing S<sub>α→β</sub>: F<sup>n<sub>α</sub></sup><sub>r<sub>α</sub></sub> → F<sup>n<sub>β</sub>· [log r<sub>β</sub>]</sup>.

An F<sub>r<sub>β</sub></sub>-arithmetic circuit C<sub>S,α←β</sub>, implementing S<sub>α←β</sub>: F<sup>n<sub>β</sub></sup><sub>r<sub>β</sub></sub> → F<sup>n<sub>β</sub>· [log r<sub>α</sub>]</sup>.

An F<sub>r<sub>β</sub></sub>-arithmetic circuit C<sup>online</sup><sub>V,α</sub>, implementing V<sup>online</sup><sub>α</sub> for inputs of n<sub>α</sub> elements in F<sub>r<sub>α</sub></sub>; an input x<sub>α</sub> ∈ F<sup>n<sub>α</sub></sup><sub>r<sub>α</sub></sub> is given to  $C_{V,\alpha}^{\text{online}}$  as a string of  $n_{\alpha} \cdot \lceil \log r_{\alpha} \rceil$  elements in  $\mathbb{F}_{r_{\beta}}$ , each carrying a bit of  $x_{\alpha}$ .

- An  $\mathbb{F}_{r_{\alpha}}$ -arithmetic circuit  $C_{V,\beta}$ , implementing  $V_{\beta}$  for inputs of  $n_{\beta}$  elements in  $\mathbb{F}_{r_{\beta}}$ ; an input  $x_{\beta} \in \mathbb{F}_{r_{\beta}}^{n_{\beta}}$  is given to  $C_{V,\beta}$  as a string of  $n_{\beta} \cdot \lceil \log r_{\beta} \rceil$  elements in  $\mathbb{F}_{r_{\alpha}}$ , each carrying a bit of  $x_{\beta}$ .

For now we take the above circuits as given; later, in Section 5 we discuss our concrete instantiations of them. Also, we generically denote by  $bits_{\alpha}$  a function that, given an input y in  $\mathbb{F}_{r_{\alpha}}^{\ell}$  (for some  $\ell$ ), outputs y's binary representation; the corresponding  $\mathbb{F}_{r_{\alpha}}$ -arithmetic circuit is denoted  $C_{\text{bits},\alpha}$ , and has  $\ell \cdot \lceil \log r_{\alpha} \rceil$  gates.<sup>14</sup>

For reference, pseudocode for the triple  $(\mathbb{G}, \mathbb{P}, \mathbb{V})$  is given in Figure 2.

<sup>&</sup>lt;sup>14</sup>More precisely, for each  $\mathbb{F}_{r_{\alpha}}$ -element  $y_i$  in the vector y, bits<sub> $\alpha$ </sub> outputs bits  $b_1, \ldots, b_{\lceil \log r_{\alpha} \rceil}$  such that  $\sum_{j=0}^{\lceil \log r_{\alpha} \rceil - 1} b_j 2^j = y_i$ , where arithmetic is conducted over  $\mathbb{F}_{r_{\alpha}}$ . Due to wrap around, some elements in  $\mathbb{F}_{r_{\alpha}}$  have two such representations; if so, bits<sub> $\alpha$ </sub> outputs the lexicographically-first one. None the less, we construct  $C_{\mathsf{bits},\alpha}$  to only check for either of these two representations, because: (i) discriminating between representations costs an additional  $\ell \cdot \lceil \log r_{\alpha} \rceil$  gates; and (ii) doing so does not affect completeness or soundness of our construction.

**The PCD generator.** The PCD generator  $\mathbb{G}$  takes as input an  $\mathbb{F}_{r_{\alpha}}$ -arithmetic compliance predicate  $\Pi$ , and outputs a key pair (pk, vk) for proving/verifying  $\Pi$ -compliance. The PCD generator works as follows: (i) it uses  $C_{H,\alpha}, C_{S,\alpha \to \beta}, C_{V,\beta}, \Pi$  to construct the circuit  $C_{pcd,\alpha}$ ; (ii) it samples a key pair,  $(pk_{\alpha}, vk_{\alpha}) \leftarrow G_4(C_{pcd,\alpha})$ ; (iii) it uses  $vk_{\alpha}, C_{S,\alpha \leftarrow \beta}, C_{V,\alpha}^{online}$  to construct the other circuit  $C_{pcd,\beta}$ ; (iv) it samples another key pair,  $(pk_{\beta}, vk_{\beta}) \leftarrow G_6(C_{pcd,\beta})$ ; and (v) it outputs  $pk := (pk_{\alpha}, pk_{\beta}, vk_{\alpha}, vk_{\beta})$  and  $vk := (vk_{\alpha}, vk_{\beta})$ .

We now describe  $C_{pcd,\alpha}$  and  $C_{pcd,\beta}$ . The circuit  $C_{pcd,\beta}$  acts as a "proof converter": it takes an input  $x_{\beta} \in \mathbb{F}_{r_{\beta}}^{n_{\beta}}$  and a witness  $a_{\beta} \in \mathbb{F}_{r_{\beta}}^{h_{\beta}}$ , parses  $a_{\beta}$  as a zk-SNARK proof  $\pi_{\alpha}$  for  $V_{\alpha}$ , and simply checks that  $C_{V,\alpha}^{\text{online}}(\mathsf{vk}_{\alpha}, C_{S,\alpha\leftarrow\beta}(x_{\beta}), \pi_{\alpha}) = 1$ . (The verification key  $\mathsf{vk}_{\alpha}$  is hardcoded in  $C_{\mathsf{pcd},\beta}$ .)

In contrast, the circuit  $C_{pcd,\alpha}$  verifies  $\Pi$ -compliance: it takes an input  $x_{\alpha} \in \mathbb{F}_{r_{\alpha}}^{n_{\alpha}}$  and a witness  $a_{\alpha} \in \mathbb{F}_{r_{\alpha}}^{h_{\alpha}}$ , parses  $a_{\alpha}$  as  $(\mathsf{vk}_{\beta}, z, z_{\mathsf{loc}}, \vec{z}_{\mathsf{in}}, b_{\mathsf{base}}, \vec{\pi}_{\mathsf{in}}, b_{\mathsf{res}})$ , and verifies that  $x_{\alpha} = C_{H,\alpha}(C_{\mathsf{bits},\alpha}(\mathsf{vk}_{\beta}) \| C_{\mathsf{bits},\alpha}(z))$  and that  $\Pi(z, z_{\mathsf{loc}}, \vec{z}_{\mathsf{in}}, b_{\mathsf{base}}) = 0$ . Moreover, if  $b_{\mathsf{base}} = 0$  (not the base case),  $C_{\mathsf{pcd},\alpha}$  also recursively verifies  $\Pi$ -compliance of previous messages: for each corresponding pair  $(z_{\mathsf{in}}, \pi_{\mathsf{in}})$  in  $(\vec{z}_{\mathsf{in}}, \vec{\pi}_{\mathsf{in}})$ , it verifies that  $C_{V,\beta}(\mathsf{vk}_{\beta}, x_{\mathsf{in},\beta}, \pi_{\mathsf{in}}) = 1$  where  $x_{\mathsf{in},\beta} = C_{S,\alpha \to \beta}(C_{H,\alpha}(C_{\mathsf{bits},\alpha}(\mathsf{vk}_{\beta}) \| C_{\mathsf{bits},\alpha}(z_{\mathsf{in}})))$ .

See Figure 2 for details. Overall, the two circuits have the following sizes: