# 适于高速高精度多级 ADC 的功耗-速率优值模型

干 奇 吴霜毅 王浩娟 覃浩洋 杨谟华 (电子科技大学微电子与固体电子学院 成都 610054)

摘 要:该文依据多级比较原理,建立了 ADC 功耗-速率优值模型。基于比较器数目最优算法,推导出多级 ADC 最优比较器数目,并提出多级 ADC 功耗-速率优值参数,从而得到可实现小功耗、高转换速率的多级 ADC 优化 结构。以 10 位精度 ADC 为例,系统级仿真结果表明:多级 ADC 中的三级 Pipelined 结构可将全 Flash ADC 功 耗降低到最小,而保持相同的转换速率;同时理论验证了以两步式结构实现多级 ADC 优于其他多步式结构。该 优值模型可应用于高速、高精度 ADC 系统结构优化。

关键词: 功耗-速率优值模型: 模数转换器: 比较器: 低功耗 中图分类号: TN432.1 文献标识码: A

文章编号: 1009-5896(2007)08-2006-03

# A Power-Conversion Rate Merit Model for High-Speed **High-Resolution ADC**

Wang Hao-juan Qin Hao-yang Wu Shuang-yi Yu Qi Ning Ning Yang Mo-hua (University of Electronic Science and Technology, Chengdu 610054, China)

Abstract: Based on multi-stage comparison, a new theory incorporating Minimum Comparator Number Algorithm (MCNA) and Power-Conversion Rate Merit Model (PCRMM) is proposed, which releases the power dissipation from limitation of comparators, sub-DACs and residual amplifiers in high-speed high-resolution ADCs. Under 10-bit ADC resolution specific, theoretical analysis shows that this theory reduces the power dissipation of Flash ADC to minimum by applying 3-stage Pipelined ADC, while keeping ADC high-speed, and it also proves that two-step ADC is better than other type of multi-step ADC. This new theory can be used in designing and developing high-speed low-power ADCs.

Key words: Power-Conversion Rate Merit Model (PCRMM); ADC; Comparator; Low-power

#### 1 引言

随着无线通信以及数字信号处理技术的飞速发展,高速 高精度模数转换器(ADC)广泛应用于无线通信终端等便携 式数字信号处理系统中。基于片上系统(SoC)的研发理念, ADC功耗已经成为制约系统性能的关键之一[1,2]。开发可嵌入 式高速高精度、低功耗ADC已成为一项具有挑战性的任务。

在众多的ADC结构中, Flash ADC速度最快, 但是功耗 大、晶体管多、芯片面积大,难以嵌入SoC芯片。分辨率为n位的全Flash结构ADC需要2<sup>n</sup>-1个比较器,并且随着分辨率 的提高, 比较器的个数将呈指数增长。为减少比较器个数, 包括多步式 ADC(Multi-step ADC) 和流水线式 ADC (Pipelined ADC)的多级ADC(Multi-stage ADC)结构得以发 展应用,前者采用多步比较方式缩减ADC功耗,后者则通过 分时、分级处理机理实现对模拟信号的量化。然而多级ADC 还需要引入子DAC、残差放大器和减法器等单元,限制了整 个ADC系统的功耗的有效降低,因而需要对其结构和功耗的 折衷做深入研究。

本文提出多级 ADC 结构比较器数目最优算法和功耗-速 率优值模型,对 ADC 功耗、转换速率与比较器数目之间的 关系进行理论分析。最优算法通过分析多级比较器各级精度 与 ADC 总比较器数目间的函数关系,推导出最小比较器数 目计算公式。源自最小比较器数目算法的优值模型,综合考 虑了 ADC 结构、功耗与转换速率之间的相互制约关系,应 用功耗-速率优值量化多种影响因素之间的折衷,提供了高速 高精度 ADC 功耗和转换速率的折衷方案。

# 比较器数目最优算法

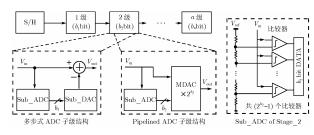

比较器的数目是影响ADC功耗的主要因素,应用多级比 较的方式可以有效减小比较器的数目<sup>[2, 3]</sup>。在ADC分辨率和 转换级数已确定的情况下,每级的精度如何分配决定着ADC 系统总的比较器数目。换而言之,比较器数目存在最优算法。 如图 1 所示, n位分辨精度ADC可分为a级对采样/保持电路 的输出信号作量化,而具体的子级结构可依据不同ADC结构 有所区别。例如,对于多步式ADC结构,其子级结构包括子 ADC, 子DAC和减法器; 而对于Pipelined ADC结构, 其子 级由子ADC和MDAC构成。然而其中的子ADC可以采用相 同的结构。

图 1 多级 ADC 结构框图

(包括多步式 ADC 和流水线 ADC 子级结构)

设每级分辨率相应为 $b_1$ ,  $b_2$ ,…,  $b_a$ , 则可得 $n=b_1+b_2$ +…+ $b_a$ , 所用比较器个数m为 ( $2^{b_1}+2^{b_2}+2^{b_3}+\dots+2^{b_a}$ -a)。由柯西不等式,可得

$$m > a \cdot 2^{n/a} - a = a \cdot (2^{n/a} - 1) \tag{1}$$

显然,当分辨率 n 和级数 a 为定值时,比较器个数 m 存在最小值。

令  $n=a\cdot b+c$ , 其中 a 为级数, b 为 n 除以 a 的商, c 为余数。则式(1)可表示为

$$m > a \cdot (2^{(a \cdot b + c)/a} - 1) \tag{2}$$

于是,当c=0 时,由式(2)可得, $m \ge a \cdot (2^b-1)$ ,即当 $n=a \cdot b$  时,每级精度取b位,比较器个数m取最小值;当 $c \ne 0$  时, $m \ge a \cdot 2^b + a \cdot 2^b (2^{c/a} - 1) - a$ 。可证明, $(a-c) \cdot 2^b + c \cdot 2^{b+1} - a$ 为最小整数。即当n/a商b余c时,其中c级精度都取为b+1,a-c级精度都取b,则此时m取最小值。对比上述两种结果,可知式(3)具有通用性,即

$$m_{\min} = (a - c) \cdot 2^b + c \cdot 2^{b+1} - a \tag{3}$$

由以上分析可得,优化后比较器个数 m最小值仅与 n, a 的取值有关,与各子级的具体结构无关。对比图 1 中的多步式 ADC 结构和 Pipelined ADC 结构,二者的子级均包含相同的子 ADC,而比较器仅与子 ADC 相关。因此上述基于子 ADC 结构的比较器数目最优算法适用于多步式 ADC 结构和 Pipelined ADC 结构。

# 3 功耗-速率优值模型

## 3.1 符号定义

将采样/保持单元的功耗表示为 $P_{\rm S/H}$ ,子DAC功耗为 $P_{\rm sub\_DAC}$ ,减法器功耗为 $P_{\rm subtractor}$ ,MDAC功耗为 $P_{\rm MDAC}$ ,比较器功耗为 $P_c$ 。以 $P_c$ 为单位,可表征各单元模块之间的功耗比例关系。 $P_{\rm sub\_DAC}$ 与 $P_{\rm subtractor}$ 之和就是 $P_{\rm MDAC}$ ,而采样/保持电路因结构与MDAC相似,所以其功耗也与 $P_{\rm MDAC}$ 相近。因此定义功耗比例系数 $R_P$ 如下, $R_P$ 合理的取值范围为 $10\sim20^{[3,4]}$ .

$$R_{P} = \frac{P_{\text{sub\_DAC}} + P_{\text{subtractor}}}{P_{c}} = \frac{P_{\text{MDAC}}}{P_{c}} = \frac{P_{\text{S/H}}}{P_{c}}$$

(4)

#### 3.2 功耗抑制比

图 1 中左下角的虚线框图为多步式 ADC 的子级结构。 第 1 步到 (a-1) 步子级结构完全相同,而最后一级由于不输 出模拟信号,无需子 DAC 和减法器单元。可见,该多步式 ADC 具有 1 级采样/保持单元,a 级子 ADC,(a-1) 级子 DAC 和(a-1) 级减法器单元。因此其功耗可以表示为

$$P_{\text{Multi\_Step}} = P_{\text{S/H}} + (a - 1) \cdot \left(P_{\text{sub\_DAC}} + P_{\text{subtractor}}\right) + m \cdot P_c$$

$$= (a \cdot R_p + m) \cdot P_c \qquad (5)$$

同理,根据图 1 中 Pipelined ADC 子级结构框图,也可得到其功耗表达式:

$$\begin{split} P_{\text{Pipeline}} &= P_{\text{S/H}} + (a-1) \cdot P_{\text{MDAC}} + m \cdot P_c \\ &= (a \cdot R_P + m) \cdot P_c \end{split} \tag{6}$$

对比式(5)和式(6),可见两种多级ADC结构具有相同的功耗计算公式。其中m与n,a的取值有关,当ADC总分辨精度n确定后,m为a的递减函数。因此,多级ADC的总功耗仅与级数a和比例系数 $R_P$ 相关。当a=1 时,多级ADC即Flash ADC,其比较器数目最多,且无需MDAC等单元电路;当a与总精度n一致时,所需的比较器数目最少,但其余电路模块最多,且其功耗与 $R_P$ 取值相关。显然为实现多级ADC最小功耗,存在最优的比较器级数。

为归一化表示功耗,以 Flash 结构(a=1)ADC 功耗为基准,定义 ADC 功耗抑制比(Power Reduction Ratio, PRR) 为

ADC功耗抑制比=

$$\frac{\text{ADC功耗}(a)}{\text{ADC功耗}(a=1)} = \frac{a \cdot R_p + m}{R_p + 2^n - 1}$$

(7)

功耗抑制比越小表示 ADC 功耗越小。

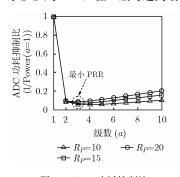

根据式(7),以 10-bit总转换精度为例,图 2 比较了取不同 $R_p$ 时多级ADC的功耗抑制比。从图中可以得到,当 $R_p$ 为 10,多级ADC的最优级数为 3,其主要模拟单元的功耗仅为 Flash结构ADC的 5.71%。随 $R_p$ 增大,功耗抑制比也有所增大,当 $R_p$ 取 20 时达到 8.53%。具体数据列于表 1。

表 1 Pipeline ADC 功耗抑制比

| Pipeline ADC | RP=10 | RP=15 | RP=20 |

|--------------|-------|-------|-------|

| 功耗抑制比        | 5.71% | 7.13% | 8.53% |

| 最优级数         | 3     | 3     | 3     |

### 3.3 转换速率抑制比

尽管多步式 ADC 与 Pipelined ADC 有相同的功耗抑制 比曲线,但前者仅分段量化输入信号,其转换速率反比于系 统级数;后者依靠流水线处理方式,以牺牲系统转换延迟为 代价,使得总体 ADC 转换速率与级数无关。

在采用相同比较器前提下,以单级比较器比较周期 $t_c$ 为基准,可量化多级ADC的转换速率。一般地,ADC时钟的占空比为 50%,采样周期与比较周期各占用 1/2 时钟周期。

对于多步式ADC,若在比较周期内完成a级比较,则比较周期须相应延长至 $a\cdot t_c$ ,总的时钟周期也需要延长至 $a\cdot 2t_c$ 。以Flash ADC转换速率 $(1/2t_c)$ 归一化的多步式ADC转换速率抑制比为

多步式ADC转换速率抑制比=

$$\frac{\text{ADC转换速率(a)}}{\text{ADC转换速率}(a=1)} = \frac{1}{a}$$

鉴于多步式 ADC 的转换速率随级数增大而减小,为保证高转换速率,通常采用两步式 ADC 结构。

对于 Pipelined ADC,各级同步工作,总转换速率与子级转换速率一致。子级通常采用含闭环运算放大器的开关电容结构,其转换速率主要由该单元电路的速度决定,而与级数 a 无关。级数的增加仅延长转换延迟时间。不考虑转换延迟,Pipelined ADC 的转换速率抑制比恒为 1 ,表示为

Pipelined ADC 转换速率抑制比 =

$$\frac{\text{ADC转换速率}(a)}{\text{ADC转换速率}(a=1)}$$

= 1 (9)

#### 3.4 功耗-速率优值

针对功耗和转换速率的变化趋势,在设计低功耗、高速高精度 ADC 时,需要对功耗和转换速率折衷。因此可定义功耗-速率优值参数(Power Conversion Rate Merit, PCRM)为

功耗-速率优值 =

$$\frac{\text{ADC功耗抑制比}}{\text{ADC转换速率抑制比}}$$

(10)

根据式(10), 功耗低而转换速率高的 ADC 结构可得到较小的 PCRM。这意味着 PCRM 低的 ADC 在消耗固定单位的 功耗情况下,具有较高的转换速率,功耗对速率的效率比较高。当优值达到最小时,功耗不一定最低,但固定单位的功耗可以实现最高的转换速率。

图 3 是Pipelined ADC与Multi-step ADC的功耗-速率优值曲线。其中 $R_P$ 值取为 20。多步式ADC受转换速率影响较大,因而优值曲线变化明显。当以常见的两步式结构实现多步比较时,曲线取得最优值,为 19.56%;当比较级数超过 3 级,优值曲线快速上升,甚至超过 1,此时多步式ADC的转换速率接近逐次逼进型ADC,不再适于高速ADC应用。流水线结构多级ADC得益于分时处理机制,其优值始终低于多步式ADC,在 3 级时达到最小,为 8.53%。

图 2 ADC 功耗抑制比 (Power reduction ratio)曲线图

图 3 多级 ADC 功耗-速率优值曲线

根据优值曲线图,高速高精度 ADC 设计中采用 Pipelined ADC 结构可以在不影响转换速率的前提下有效 降低 ADC 功耗。随着级数增加,优值稍有回升,然而始终小于 20%。多步式 ADC 受转换速率限制,一般仅采用两步式结构。

# 4 结束语

本文提出多级ADC比较器数目最优算法,进而建立功耗-速率优值模型。该模型综合考虑了ADC结构、功耗与转换速率之间的相互制约关系,提供了高速高精度ADC功耗、结构和转换速率间的折衷方案。以 10-bit精度ADC为例,进行系统级仿真,结果表明:(1) 对比功耗-速率优值,两步式ADC在多步式ADC结构中性能最优,PCRM最低;(2)对于Pipeline ADC, $R_P$ 取典型值  $10\sim20$  时,三级流水线结构的功耗抑制比最高,且不会降低转换速率,其功耗效率最优。该优值模型可应用于高速、高精度ADC系统级结构优化。

# 参考文献

- Gray P R and Meyer R G. Future directions in silicon IC's for RF personal communications. Proc. IEEE Custom Integrated Circuits Conf., Santa Clam. CA, USA, May 1995.

- [2] Stojcevski A, Singh J, and Zayegh, et al.. Performances analysis of a CMOS analog to digital converter for wireless telecommunications. Proc. IEEE Devices & Systems Conf, ISIC-2001, Singapore, 2001: 59–62.

- [3] Lewis S H. Optimizing the stage solution in pipelined, multistage, analog-to-digital converters for video-rate applications. IEEE Trans. on Circuits and Systems-II: Analog and Digital Signal Processing, 1992, 39(8): 516–523.

- [4] Kwok P T F and Luong H C. Power optimization for pipeline analog-to-digital converters. *IEEE Trans. on Circuits and System-II: Analog and Digital Signal Processing*, 1999, 46(5): 549–553.

吴霜毅: 男,1981年生,硕士生,从事模数混合信号集成电路领域的研究,目前的研究方向是Pipeline ADC.

于 奇: 男, 1973年生, 副教授, 主要从事SoC领域研究.

王浩娟: 女,1981年生,硕士生,从事模数混合信号集成电路领域的研究.

覃浩洋: 男,1977年生,硕士生,从事模数转换器后台校正算法和技术的研究.

宁 宁: 男,1981 年生,博士生,从事模数信号集成电路的研究. 杨谟华: 男,1944 年生,教授,博士生导师,主要从事集成电路的研究.