Vol.32

2006年8月 August 2006

Nº 16 工程应用技术与实现。

文章编号: 1000-3428(2006)16-0235-02

文献标识码: A

中图分类号: TP332.3

# 优化帧频控制的 LCD 控制器 IP 的设计与验证

汪 翼,沈海斌,樊俊锋

(浙江大学超大规模集成电路设计研究所,杭州 310027)

摘 要:随着 LCD 在嵌入式系统中的广泛应用,LCD 控制器 IP 成为 SoC 芯片中的一个重要部件。文章介绍了一种支持 TFT 和 STN 屏的 LCD 控制器设计。该设计使用了基于空间散列的帧频控制算法以优化 LCD 显示图像质量,并使用两级缓存结构以保证稳定的输出数据流。 文章同时给出了模块化可配置的自动验证方案,并在FPGA上实现了该设计。

**关键词:**LCD;控制器;帧频控制;验证

# **Design and Verification of LCD Controller IP Using Optimal Frame-rate Control**

WANG Yi, SHEN Haibin, FAN Junfeng

(Institute of VLSI Design, Zhejiang University, Hangzhou 310027)

[Abstract] As the LCD player is widely used in the embedded system, LCD controller IP becomes an important component of SoC. This paper introduces a design of LCD controller which supports TFT and STN LCD. This design uses a frame rate control algorithm based on space-hash to improve the quality of the LCD display. It uses two-level buffer structure to ensure steady output flow. The paper also introduces a modularized configurable automatic verification scheme. This design has been implemented on FPGA.

【Key words】LCD; Controller; Frame-rate control; Verification

嵌入式系统设计中, LCD以其低功耗、体积小的特点得 到了越来越多的应用[1]。针对嵌入式应用的SoC芯片中,一个 专门的支持各种类型和大小LCD屏的控制模块可以有效满足 各种实际应用需求,把MCU从繁琐的数据处理中解放出来, 从而极大地优化系统性能。同时, STN型LCD屏由于其驱动 技术和颜色显示方式的原因,图像质量不高,尤其存在图像 闪烁的问题<sup>[2]</sup>。这个问题是由STN屏工艺技术造成的,但可 以通过在LCD控制器中对帧频控制方式优化得到改进。

基于上述考虑,我们设计了一个基于 AMBA AHB 总线, 支持 TFT 和 STN 两种主流 LCD 显示屏,可配置最高 24bpp 真彩色,最高支持 1 024×1 024 点阵显示屏,自带 DMA 的 LCD 控制器。为了防止 STN 屏显示时容易出现的屏幕闪烁现 象,采用了空间散列的方法优化帧频控制(FRC);为了保证 LCD 输出数据流稳定不中断,采用了输入输出两级缓存的结 构,以防止出现显示数据下溢。

# 1 系统结构及模块设计

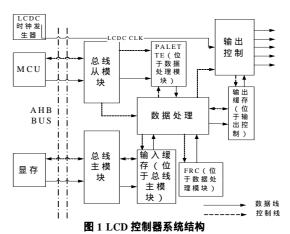

整个设计可分为 4 个大的模块:总线从模块,总线主模 块,图像数据处理,输出控制。LCD时钟发生被置于SoC级 时钟发生器中实现,以利于系统级 DFT 实现。系统结构如图 1 所示。

#### 1.1 总线从模块和总线主模块

总线从模块从 AMBA AHB 总线上接受 MCU 对 LCD 控 制器寄存器的配置,以控制 LCD 控制器支持的 LCD 屏类型、 大小、色深、行扫描帧扫描方式和刷新频率等。总线从模块 还负责向 MCU 发出画面切换中断,一旦总线主模块读取完 一幅画面的所有显示数据,从模块向 MCU 发出中断请求, 指示 MCU 修改显存基址寄存器以实现动态画面显示。

总线主模块执行 DMA 操作,按照配置寄存器的设定从 指定分配为显存的位置读取显示数据,保存在输入缓存中。 输入缓存是一个 32 x 32 单时钟 FIFO, 一旦输入缓存进入半 空态,主模块便发出新的总线突发模式(burst)读请求,读入 下一批显示数据。

# 1.2 数据处理模块

数据处理模块从输入缓存读取原始的显存图像数据,按 照从模块中寄存器中颜色深度和 LCD 面板类型配置进行相 应的数据处理,结果存入输出缓存中。数据处理的基本步骤

基金项目: 国家 "863" 计划基金资助项目(2003AA141050/2003AA 1Z1060)

**作者简介:**汪 翼(1981—), 男, 硕士生, 主研方向: SoC 设计及验 证;沈海斌,副教授;樊俊锋,硕士生

**收稿日期:**2005-10-26 E-mail: wanggy@vlsi.zju.edu.cn 为 3 步:32bit 显示数据按颜色深度分组;访问调色板寄存器及帧频控制;显示数据重组。调色板是一个 256 × 32 的寄存器组,保存 256 级颜色信息,在控制器开始工作前由 MCU设置该寄存器组颜色值。不同的显示模式有不同的中间处理过程,TFT 模式下访问调色板寄存器组得到颜色值后可直接存入输出缓存,STN 模式下得到颜色值后还需要进行帧频控制。由于使用 256 级调色板,8bpp 色深以上显示不必经过访问调色板,可直接进入后继处理。

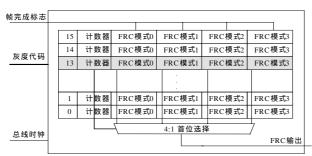

STN型LCD屏通过控制像素明灭频率即帧频控制来实现灰度进而实现彩色<sup>[2]</sup>,这种方式容易出现图像闪烁<sup>[3,4]</sup>,为此采用了基于空间散列的帧频控制。造成图像闪烁的抖动噪声来自于像素在相邻的帧之间相似的变化。如果在第 1 帧里,所有的像素都是明,而在第 2 帧里,所有的像素都是灭,这样的抖动最大。要减少屏幕抖动噪声,则需要控制每一帧的明灭像素的数量,使得其平均值相当。为了做到这一点,对相同灰度级的像素按照扫描时出现的顺序分组,分配以不同的明灭模式,把本来可能要显示在同一帧内的相同状态(如都要显示为明)分散到不同的帧中,错开其明灭的时间,以去除可能出现的抖动。例如,对同样灰度值为 12 的像素点,分别分配以 0111、1011、1101 和 1110 4 种明灭模式。

帧频控制模块结构如图 2 所示。每一级灰度单元有 4 组 FRC 模式和一个 2 位计数器。每组 FRC 模式结构为一个线性循环移位器,在启动时被赋予初始值,每帧完成时循环移动一位。计数器在一帧开始时清零,每次该灰度级被选中后加 1。工作时,像素灰度代码输入 FRC 模块,对应的灰度单元被选中,由计数器值控制从 4 组移位器首位值中选择输出一位作为帧频调制结果。这样,计数器将同样灰度级像素按扫描顺序分为 4 组,每组按明灭频率相同而明灭排列顺序不同的模式进行帧频控制,显示时仍然为同样的灰度,但是每帧明灭像素点数分布更为均匀。

图 2 帧频控制模块结构

处理完成后的显示输出数据被保存在输出缓存中。该缓存是一个 32×24 双时钟异步 FIFO,使用格雷码地址计数器以避免异步时钟可能造成的记数错误。当 FIFO 中空单元数量大于 8 时即向控制逻辑发出指示,要求继续处理新的显存数据填满输出缓存。如前所述,本设计中使用了两级缓存以保证输出数据流不被打断,这是基于如下考虑:(1)一次总线读需要不确定的总线仲裁及设备响应时间,需要一级输入缓存保证数据处理模块在需要时始终能得到显示数据;(2)控制器支持的多种显示模式需要的各不相同的数据处理时间;(3)LCD 输出数据流不是均衡的,一旦开始则会连续发送一行数据,然后进入一段等待期。使用两级的缓存结构保证了即使在极端的情况下,仍能提供给 LCD 稳定不中断的输出流。

#### 1.3 输出控制

输出模块按照屏类型及大小产生行扫描信号、帧扫描信

号以及输出使能信号,并在适当的时候把输出缓存中的数据按照正确的格式输出。TFT 屏与 STN 屏有着完全不同的输出时序及数据形式,可通过两组并行的有限状态机 FSM 和一个选择器控制输出时序信号,将输出缓存数据直接输出(TFT)或分组输出(STN)。

# 2 设计验证

对 LCD 控制器设计的验证,包括代码质量检查、总线行为和输出时序验证以及输出数据检查3大块。代码质量检查使用 Synopsys 公司的 LEDA、CoverMeter、PrimeTime、DFTC等工具对 RTL 代码风格、DFT、测试覆盖率等方面进行评估,可提前发现代码中隐含的问题,提高代码质量。

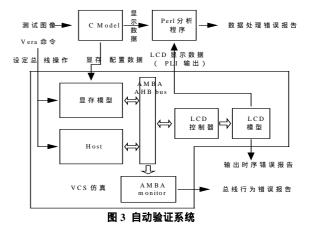

LCD控制器复杂的总线行为和大量的图像数据处理要求自动化的验证过程。为此,我们使用Synopsys DW VIP<sup>[5]</sup>模块,设计可配置的Verilog LCD模型,C语言控制器模型和Perl语言分析程序,搭建了一个模块化,可配置的自动验证系统,如图 3 所示。开始仿真之前,通过VERA指令的方式设定VIP的总线行为,配置LCD模型为本次验证针对的屏类型和大小,并将测试图像交由C Model处理生成一份用来配置显存的图像数据,一份交给Perl程序的显示数据。开始仿真后,AMBAMonitor模块监视总线上的信号,检查总线行为是否符合AMBA协议并即时生成错误报告;LCD模型接受控制器显示输出,检查时序并生成错误报告;显示输出数据在仿真过程中通过PLI接口传给Perl分析程序,得到数据处理错误报告。上述验证系统可以方便地指定生成测试向量,自动检查结果正确性,并准确地定位错误所在,迅速高效地验证LCD控制器的功能。

#### 3 设计实现

我们使用 Xilinx VertexII3000 FPGA 器件,用简单可综合的 MCU,显存和总线模型搭建了一个 FPGA 测试系统,实现了 LCD 控制器,并用其正确驱动了 SHARP LQ0573 TFT型 LCD 和 ALPS LFUBK909 STN型 LCD。LCD 控制器使用了FPGA 上 5%的 LUT 资源,总线时钟可达到 135MHz。

ASIC 实现采用 SMIC .18 标准单元库,使用 Synopsys EDA 工具对其进行综合和布局布线 控制器包括调色板 RAM 在内的面积为  $1.43 \,\mathrm{mm} \times 1.61 \,\mathrm{mm}$  ,总线时钟可达到  $200 \,\mathrm{MHz}$ 。

#### 4 结论

本文讨论了一种基于 AMBA 总线,采用空间散列帧频控制和两级缓存结构的 LCD 控制器 IP 设计,并给出了一种模块化可配置的自动测试方案。FPGA 测试表明该设计可以正确地驱动控制 TFT 和 STN 面板,并具有高速度和面积小的特点。 (下转第 252 页)