Vol.33

**Computer Engineering**

No.6 工程应用技术与实现。

文章编号: 1000-3428(2007)06-0239-03

文献标识码: A

中图分类号: TP301

# 基于对可编程逻辑块建模的 FPGA 通用装箱算法

倪 刚,童家榕,来金梅

(复旦大学张江校区专用集成电路与系统国家重点实验室,上海 201203)

摘要:装箱是 FPGA 工艺映射中的最后一步流程。该文提出了一种全新的对 FPGA 可编程逻辑块进行功能级建模的方法,并给出了基于 此建模的通用性装箱算法 FDUPack。实验中应用该建模方法对几种不同类型的 FPGA 的逻辑块进行建模,并使用装箱算法将大量的测试电 路装箱到这些不同的逻辑块中,经过与已有的针对某一特定结构的装箱算法比较,该算法体现了很好的通用性。

**关键词:** 工艺映射;装箱算法;建模;现场可编程门阵列

# Universal Packing Algorithm for FPGA Based on Logic Block Modeling

NI Gang, TONG Jiarong, LAI Jinmei

(State Key Laboratory of ASIC & System, Fudan University (Zhangjiang Branch), Shanghai 201203)

[Abstract] Logic block packing is the last procedure of FPGA technology mapping. A novel function level modeling method for programmable logic block is proposed. Based on this modeling, a universal logic block packing algorithm FDUPack is presented. In the experiment some logic blocks of different types of FPGAs are modeled, and by using the packing algorithm a lot of benchmarks are packed to these different types of logic blocks. Compared with the existent logic block specific packing algorithms, FDUPack is structure-independent and universal.

**Key words** Technology mapping; Packing algorithm; Modeling; Field programmable gate array

### 1 概述

逻辑块(Logic block)是现场可编程门阵列(FPGA)中实现 用户设计电路的部件。各种型号的商用 FPGA 的逻辑块结构 是不同的,用户设计电路的功能可以在各种不同结构的逻辑 块中实现。现在比较流行的一大类 FPGA 采用的是静态随机 存储器(SRAM)编程工艺,本文讨论的 FPGA 也属于这一类。

FPGA 工艺映射是将用户设计电路的门级网表划分成很 多小块,每一小块的逻辑功能都可以用 FPGA 的逻辑块来实 现。工艺映射又分为映射(Mapping)和装箱(Packing)两个子步 骤。映射子步骤的目标是把基本门级网表转换成由查找表 (look-up table, LUT)、多路选择器(multiplexer, MUX)和触发器 (flip-flop, FF)等电路功能元件组成的网表;装箱子步骤的目 标就是在考虑约束(如一个逻辑块中所容纳的查找表、不同的 输入信号和时钟的数目等)情况下,把 LUT、MUX 和触发器 等电路功能元件进行组合,尽可能地放到一个逻辑块中。装 箱完成后就可以进行逻辑块的布局。

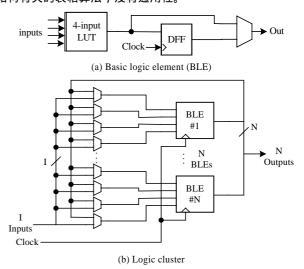

对于映射子步骤,目前提出了很多成熟的算法。比如, 把基本门转换成LUT这一方向,有FlowMap算法[1]等;把基 本门转换成MUX这一方向,有Proserpine算法[2]等。所有映射 算法,都和FPGA的逻辑块的具体结构无关,因此对于不同结 构的逻辑块来说是通用的。对于装箱子步骤,已有的装箱算 法T-VPack可以有效地处理基于BLE(Basic Logic Element)组 成的簇(cluster)结构的逻辑块(如图 1 所示)的装箱问题。 T-VPack算法将经过映射子步骤处理后的用户网表中的LUT 和DFF首先——配对打包到BLE中,然后再将多个BLE装箱到 一个簇结构的逻辑块里。UCLA开发了RASP<sup>[4]</sup>系统,其中集 成了3种与FPGA逻辑块结构有关的装箱模块,分别可以处理 Xilinx公司的XC3000 系列和XC4000 系列FPGA芯片的逻辑

块,以及Altera公司的FLEX-8000系列FPGA芯片的逻辑块的 装箱问题。上述这些装箱算法的共同局限在于,它们都是专 门针对某一具体结构的逻辑块所设计的,因此都是与逻辑块 结构有关的装箱算法,没有通用性。

图 1 由 BLE 组成的簇结构的逻辑块

本文提出了一种对 FPGA 的逻辑块结构的功能级建模方

基金项目:上海应用材料科技合作共同计划(AM0406);国家自然科 学基金资助项目(60076014)

作者简介:倪 刚(1981-),男,硕士生,主研方向:现场可编程门 阵列(FPGA)的工艺映射算法和FPGA软件系统设计;童家榕,教

授;来金梅,副教授

收稿日期:2006-05-30 E-mail: nigang@fudan.edu.cn 法,并基于此方法,提出了一种功能元件和线网双重匹配的 装箱算法 FDUPack,从而解决了与逻辑块的具体结构无关的 通用的逻辑块装箱问题。

# 2 可编程逻辑块的功能级建模

FPGA 的逻辑块的结构可分为物理结构和功能结构两个范畴。其中物理结构与 FPGA 的版图相关,功能结构与 FPGA 所实现的逻辑相关。在逻辑块装箱这一步,只需考虑逻辑块的功能结构。因此,下面讨论的建模方法也是针对逻辑块的功能结构进行的。

定义1 开关多路选通器(Switch MUX): 它是逻辑块内部由编程点(存储编程信息的 SRAM)控制,起开关作用的多路选通器。开关多路选通器不分担逻辑块的任何逻辑功能。

**定义 2** 功能元件(Function Device):在逻辑块内部典型的、有特定的逻辑功能的电路元件,如 LUT、MUX、触发器、专用进位链(Carry Chain)等。

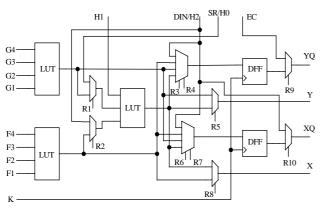

逻辑块的功能结构通常就是由一定数量的开关多路选通器和功能元件连接组成。不同的逻辑块中的功能元件的数量和种类、开关多路选通器的数量、元件间的连接都是不相同的。因此,可以用功能元件和开关多路选通器这二大类元件间的连接关系来描述一个逻辑块的功能结构。图 2 是Xilinx公司XC4000 系列FPGA逻辑块的功能结构图<sup>[5]</sup>,其中的功能元件有 2 个 4 输入LUT、1 个 3 输入LUT、2 个触发器,还有数个开关多路选通器(由编程点R1~R10 控制)。

定义 3 样本电路 (Pattern Circuit): 在逻辑块内部,配置各个开关多路选通器上的编程点的值(设定为 0 或者 1),每个开关多路选通器有一路选通,这样得到的功能元件间的一种确定的连接称为逻辑块的一个样本电路。

图 2 XC4000 的逻辑块功能结构

由此可见,逻辑块的功能结构是功能元件和开关多路选通器间的连接,而样本电路是 FPGA 经过编程配置后逻辑块中的功能元件间的连接。每个样本电路的功能就是逻辑块在编程后所能实现的一种逻辑功能。对于同一个逻辑块,在多组不同的编程值下可以得到多个样本电路。一个逻辑块和它的样本电路之间是一对多的关系。

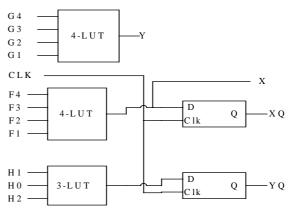

用网表描述逻辑块后,对逻辑块进行分析,可以得到它所有的有效样本电路。图 3 中显示了 XC4000 的逻辑块在编程点 R1~R10=0010101111 值下的样本电路。而 XC4000 的逻辑块的所有有效样本电路和编程点值的对应关系见表 1。

逻辑块的功能模型,也就是该逻辑块的所有有效样本电路的描述,而每个样本电路自身又是一些相同和不同的功能元件间的确定连接。这就是逻辑块功能级建模的基本想法。

图 3 XC4000 逻辑块在 0011001111 编程值下的样本电路

表 1 XC4000 逻辑块的有效样本电路和编程点值的对应表

| R1~R10 值   | 样本电路说明                            |

|------------|-----------------------------------|

| 0011001111 | 4-LUT+DFF 组合/时序输出,3-LUT+DFF 时序输   |

|            | 出,4-LUT 组合输出                      |

| 0010101111 | 4-LUT+DFF 组合/时序输出,4-LUT+DFF 时序输   |

|            | 出,3-LUT 组合输出                      |

| 0011001011 | 3-LUT+DFF 组合/时序输出,4-LUT+DFF 时序输   |

|            | 出,4-LUT 组合输出                      |

| 1111101111 | 4-LUT+DFF 组合/时序输出和 4-LUT 组合输出至    |

|            | 3-LUT, 3-LUT+DFF 组合/时序输出          |

| 1011101111 | 4-LUT+3-LUT+DFF 组合/时序输出,4-LUT+DFF |

|            | 组合/时序输出,                          |

| 1110101111 | 2 个 4-LUT 都输出到 3-LUT,并分别输出到 1 个   |

|            | DFF                               |

| xx10001111 | 4-LUT+DFF 组合/时序输出,4-LUT+DFF 组合/时  |

|            | 序输出                               |

| xx00xxxx1x | 1 个 DFF                           |

## 3 通用装箱算法 FDUPack

上面介绍了可编程逻辑块的功能级建模,而建模的最终目的是为了实现通用性的装箱算法。在通用性装箱算法中,逻辑块的功能模型,也就是逻辑块的所有有效样本电路的描述,作为一个输入项。用户设计电路的网表是通用性装箱算法的另一个输入项,在经过工艺映射中的映射子步骤后,已经从基本门级被转换到功能元件级。本文提出的通用性装箱算法 FDUPack,是基于对可编程逻辑块的功能级建模,目的是把用户设计电路的网表从功能元件级逻辑等价地装箱至逻辑块级。装箱完毕后用户设计电路的网表仅仅由逻辑块组成。

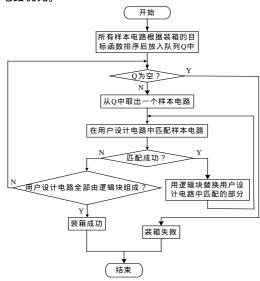

用户设计电路和逻辑块的样本电路都是由功能元件组成的,FDUPack 算法就是在用户设计电路中寻找与逻辑块的每个样本电路同构的子电路,这个过程称为匹配。匹配成功的话就把同构的子电路中的功能元件和内部线网删去,并加入一个逻辑块作为新的电路元件,连接逻辑块和边界线网(逻辑块的引脚对应于样本电路的边界线网)。重复上述过程,直到用户电路全部由逻辑块组成,装箱完成。FDUPack 的整体流程如图 4 所示。

装箱的目标函数决定了和用户设计电路匹配时样本电路 的先后顺序。

(1)以面积最小为目标。面积最小,就是要装箱完成后的逻辑块级用户电路中逻辑块个数最少,因此匹配顺序就是含功能元件个数多的样本电路优先。

(2)以时延最小为目标。时延最小,就是要装箱完成后的逻辑块级用户电路中的关键路径上经过的逻辑块个数最小,因此匹配顺序就是样本电路的关键路径上功能元件个数多的

样本电路优先。

图 4 FDUPack 算法的顶层流程

"在用户设计电路中匹配样本电路"是 FDUPack 装箱算法的核心,它采用在样本电路和用户电路中作功能元件匹配和线网匹配的遍历。遍历过程中两个当前功能元件或线网不匹配时则终止匹配过程,返回匹配起点,当整个样本电路都已遍历完且没有碰到不匹配,就认为找到了同构的子电路。算法如下:

- (1)在用户电路中匹配样本电路

- 1)从用户电路和样本电路中各选择一个功能元件,把它们的关系放入待匹配队列,作为匹配起点;

- 2)从待匹配队列中取出一个关系;

- 3)关系若是功能元件,就进行功能元件匹配;

- 4)关系若是线网,就进行线网匹配。

- (2)功能元件对的匹配

- 1)检查两个功能元件的类型是否一致,输入输出管脚数目是否一致;

- 2)都一致的话,两个功能元件存在匹配可能,把这两个功能元件的对应关系推入已匹配堆栈,把与这两个功能元件各对应管脚相连的未遍历的到的线网的对应关系放入待匹配队列:

- 3)反之不一致的话,返回不匹配。

- (3)线网匹配

- 1)除样本电路的边界线网外,两个线网连接的管脚数量和所属功能元件类型是否一致,若两管脚所属元件是已匹配元件对,再看管脚的等价性是否一致;

- 2)都一致的话,两个线网存在匹配可能,把这两个线网的对应关系推入已匹配堆栈,把与这两个线网相连的未遍历到的元件的对应关系放入待匹配队列;

- 3)反之不一致的话,返回不匹配。

### 4 实验和总结

通用装箱算法FDUPack在Windows环境下用C++语言实现。实验选取了 3 种逻辑块中:(1)学术界研究较多的BLE(图1(a));(2)Xilinx公司XC4000系列芯片的CLB(图2);(3)复旦大学自主研发的FPGA芯片FDT200k的可编程逻辑单元[6]。测试电路网表选用了MCNC的组合电路测试网表<sup>[7]</sup>。

测试电路网表首先经过映射算法FlowMap<sup>[1]</sup>处理,然后使用下面 3 种装箱算法做装箱处理。通用装箱算法FDUPack

成功地把测试电路装箱到上述 3 种逻辑块中;T-VPack<sup>[3]</sup>是针对基于BLE组成的簇结构的逻辑块的装箱算法,因此只能把这些测试电路装箱到A中;RASP系统<sup>[4]</sup>中自带的装箱程序包lut2xc4k是针对XC4000系列的逻辑块的装箱算法,因此只能把这些测试电路装箱到B中。FDUPack、T-VPack、lut2xc4k这 3 种算法对相同的测试电路的装箱结果见表 2。

表 2 3 种装箱算法的结果 (逻辑块个数)对比

| 7 2 3 作农相异应的纪末(这再次 1 数 <i>)</i> 对比 |         |       |       |         |   |   |          |       |   |  |  |

|------------------------------------|---------|-------|-------|---------|---|---|----------|-------|---|--|--|

| 装箱算法                               | FDUPack |       |       | T-Vpack |   |   | lut2xc4k |       |   |  |  |

| 逻辑块                                | A       | В     | C     | A       | В | С | A        | В     | С |  |  |

| 9symm1                             | 89      | 46    | 84    | 89      | / | / | /        | 42    | / |  |  |

| alu2                               | 300     | 149   | 280   | 300     | / | / | /        | 132   | / |  |  |

| alu4                               | 1805    | 892   | 1756  | 1805    | / | / | /        | 766   | / |  |  |

| C3540                              | 410     | 205   | 387   | 410     | / | / | /        | 181   | / |  |  |

| C432                               | 95      | 51    | 92    | 95      | / | / | /        | 44    | / |  |  |

| C5315                              | 629     | 314   | 570   | 629     | / | / | /        | 271   | / |  |  |

| C6288                              | 741     | 371   | 422   | 741     | / | / | /        | 371   | / |  |  |

| C7552                              | 788     | 394   | 72    | 788     | / | / | /        | 336   | / |  |  |

| C880                               | 139     | 70    | 124   | 139     | / | / | /        | 65    | / |  |  |

| cordic                             | 845     | 387   | 797   | 845     | / | / | /        | 356   | / |  |  |

| count                              | 41      | 29    | 37    | 41      | / | / | /        | 21    | / |  |  |

| dalu                               | 643     | 322   | 583   | 643     | / | / | /        | 286   | / |  |  |

| des                                | 3427    | 1414  | 2672  | 3427    | / | / | /        | 1385  | / |  |  |

| frg1                               | 303     | 152   | 281   | 303     | / | / | /        | 149   | / |  |  |

| i10                                | 946     | 472   | 881   | 946     | / | / | /        | 424   | / |  |  |

| i2                                 | 79      | 39    | 79    | 79      | / | / | /        | 37    | / |  |  |

| i3                                 | 46      | 21    | 46    | 46      | / | / | /        | 21    | / |  |  |

| rot                                | 517     | 255   | 485   | 517     | / | / | /        | 227   | / |  |  |

| t481                               | 609     | 271   | 596   | 609     | / | / | /        | 267   | / |  |  |

| too_large                          | 5 522   | 2 497 | 5 166 | 5 522   | / | / | /        | 2 497 | / |  |  |

| x1                                 | 760     | 374   | 726   | 760     | / | / | /        | 358   | / |  |  |

| z4ml                               | 78      | 42    | 66    | 78      | / | / | /        | 37    | / |  |  |

从表 2 中可以看出,对于 BLE 这种结构简单的逻辑块,FDUPack 的结果和 T-VPack 相同;对于 XC4000 的 CLB,FDUPack 的结果比 lut2xc4k 稍差;然而,T-VPack 和 lut2xc4k 都是针对特定逻辑块的装箱算法,不能处理其他逻辑块,通用性上远不及 FDUPack。只要先对逻辑块进行建模,都可以用 FDUPack 算法进行装箱处理。

装箱过程是 FPGA 的工艺映射流程中与逻辑块结构有关的步骤,已有的装箱算法都是针对某一具体确定的逻辑块而设计的。本文提出了一种新颖的逻辑块功能级建模方法,采用多个样本电路来描述一个逻辑块的功能,并在此基础上提出了一种逻辑块装箱算法 FDUPack,FDUPack 算法将样本电路描述和用户设计电路的网表都作为装箱程序的输入,并在样本电路和用户设计电路间采用功能元件和线网双重匹配的方法进行装箱,因此 FDUPack 装箱算法是与逻辑块结构无关的,具有很好的通用性。FDUPack 算法在装箱结果上还可以优化,这方面将在今后工作中做改进。