**Computer Engineering**

开发研究与设计技术。

文章编号: 1000—3428(2007)12—0280—03

文献标识码: A

一 中图分类号: TP391

# 基于 Eclipse 平台的边界扫描测试软件的开发

林金晓1,陈伟男2,周学功2,彭澄廉2,吴荣泉3

(1. 复旦大学软件学院,上海 200433; 2. 复旦大学计算机与信息技术系,上海 200433; 3. 华东计算技术研究所,上海 200233)

摘要:复旦大学研制的类蜂巢结构快速样机平台(HLRESP)采用模块化结构,可以灵活配置和选择功能模块,而扫描链路的设计,以及扫描链路的完整性测试和互连测试对平台极为重要,为了满足该系统的测试和调试的需要,该文设计并实现了一个基于 Eclipse 平台的边界扫描测试软件。该软件能够自动生成测试向量,分析响应数据并准确定位故障。

关键词:边界扫描;互连测试; Eclipse; JTAG; 插件开发

# Development of Eclipse Based Boundary-scan Tester Software

LIN Jinxiao<sup>1</sup>, CHEN Weinan<sup>2</sup>, ZHOU Xuegong<sup>2</sup>, PENG Chenglian<sup>2</sup>, WU Rongquan<sup>3</sup>

(1. School of Software, Fudan University, Shanghai 200433; 2. Department of Computing and Information Technology, Fudan University, Shanghai 200433; 3. East-China Institute of Computer Technology, Shanghai 200233)

[Abstract] Honeycomb-like rapid embedded system platform (HLRESP) is developed by Fudan university. This platform is in modularized structure, and it can configure module blocks freely. For the sake of the system test and debugging, the design of boundary-scan and the integrality test and interconnect test of boundary-scan is very important to the platform. A boundary-scan tester software is designed based on Eclipse for this system test and debugging. This software can build the test vectors automatically, analyze the response data and locate fault accurately.

**Key words** Boundary-scan; Interconnect test; Eclipse; JTAG; Plug-in

# 1 概述

复旦大学研制的类蜂巢结构快速样机平台(HLRESP),具有对称的、类似蜂窝状的结构,采用了以连接为中心的设计方法。整个平台所有的功能模块围绕 FPGA 板安装,利用FPGA的可编程特性,可以灵活地设置功能部件的互连。

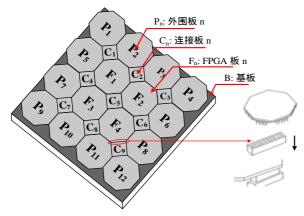

HLRESP 样机平台的硬件结构如图 1 所示,主要由基板、FPGA 板、连接板和外围功能板组成。其中,FPGA 板和外围功能板设计成正八角形,连接板是正方形的,它们都通过四周的 D-SUB 插针安装在基板上,由基板提供电源、时钟、扫描测试等全局信号。连接板上安装了复杂可编程逻辑器件(CPLD),可根据不同的应用需求,通过 CPLD 实现连接板四周的功能板之间信号的互连。外围功能板实现不同的功能应用,包括以太网通信板、A/D和 D/A 功能板、多串口通信板、RAM 和 FLASH 存储器板、LCD 显示板等。

图 1 HLRESP 样机平台的硬件结构

该样机平台采用模块化结构,扩充方便,可以灵活地构建不同规模的样机系统。这种渐增式的模块化结构同样也符合嵌入式系统中的由简单到复杂的设计原则。

平台中应用了 Altera 公司的 Cyclone 系列 EP1C6型 FPGA 和 MAX 7000AE 系列 EPM7256AE 型 CPLD 等超大规模集成 电路,并采用了多层印制板、表面贴装等技术。为了提高系统的可控制性和可观测性,根据该样机平台的特点,在系统 功能设计的同时充分考虑到测试的要求,采用 IEEE 1149.1 标准规定的边界扫描技术进行板级和系统级的可测试性设计,开发了本测试软件,用于系统的测试和调试工作。

# 2 边界扫描测试原理和算法

边界扫描测试是通过在芯片的每个I/O脚附加一个边界扫描单元(boundary scan cell, BSC) 以及一些附加的测试控制逻辑实现的, BSC 主要是由寄存器组成的。每个I/O管脚都有一个BSC,而每个BSC 有 2 个数据通道:(1)测试数据通道,测试数据输入(test data input, TDI)、测试数据输出(test data output, TDO);(2)正常数据通道,正常数据输入(normal data input, NDO)<sup>[1]</sup>。

在正常工作状态,输入和输出数据可以自由通过每个BSC,正常工作数据从 NDI 进,从 NDO 出。在测试状态,可以选择数据流动的通道:对于输入的集成电路引脚,可以选择从 NDI 或从 TDI 输入数据;对于输出的 IC 管脚,可以

基金项目: 国家自然科学基金资助项目(69873010)

**作者简介:**林金晓(1982 - ),男,硕士生,主研方向:嵌入式系统快速样机技术,硬/软件协同设计;陈伟男、周学功,博士生;彭澄廉,

教授、博导;吴荣泉,研究员

**收稿日期:**2006-09-04 **E-mail:**42053021@fudan.edu.cn

选择从 BSC 输出数据至 NDO ,也可以选择从 BSC 输出数据至 TDO。

边界扫描测试技术主要应用于 2 类测试:完整性测试和 互连测试。

#### (1)完整性测试(扫描链测试)

对于任何一个具有边界扫描设计的系统,在对系统进行 其他任何测试之前,首先对边界扫描链路的连接及工作状态 进行测试,以确保边界扫描链路本身的功能是完全正常的。

#### (2)互连测试

互连测试是引进边界扫描测试技术的一个主要原因。互连测试主要是指对电路板上器件之间互连线的测试,检测电路板级的开路、短路或者呆滞等故障。由于 HLRESP 样机中各功能板都通过接插件相互连接,必须对每个接插件进行互连测试,确保其可靠连接。

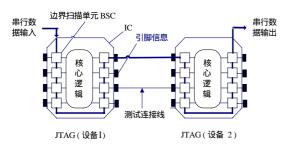

边界扫描测试应用的示意图如图 2 所示<sup>[2]</sup>。为了测试两个JTAG 设备的连接,首先将JTAG 设备 1 的某个输出测试脚的BSC置为高或低电平,输出至NDO,然后,由JTAG设备 2 的输入测试脚来捕获从管脚输入的NDI值,再通过测试数据通道将捕获到的数据输出至TDO,对比测试结果,即可快速准确的判断这两脚是否连接可靠。

图 2 边界扫描测试应用示意图

互连测试的基本算法可分为完备算法和非完备算法。其中,完备算法有走步 1 算法(walk-1)、走步 0 算法(walk-0)。走步 1 算法的初始测试矢量可以设为(1,0,0,…,0),然后让 1 顺序移位,所以称为走步 1 算法。这种算法的测试矢量个数为n,它能够检测所有固定逻辑故障、开路故障和短路故障,并且能对故障进行精确定位。而非完备算法有改良记数序列算法(MCSA)、计数/补偿算法(true/compliment)和等权值抗混迭算法等。这些算法减少了测试矢量的个数,但在诊断故障的精度和对故障的定位方面能力不如完备算法<sup>[3]</sup>。

# 3 Eclipse 平台

HLRESP 系统由软件集成开发环境(ESIDE)和硬件平台组成, ESIDE 是基于 Eclipse 平台的 IDE 工具。本软件的开发也是基于 Eclipse 平台的。Eclipse 平台是一个成熟的、精心设计的可扩展的体系结构。这个平台允许任何人构建与其环境和其他工具无缝集成的工具。

Eclipse 是一个基于插件的体系结构。提供了 PDE (plug-in development environment)用于开发者创建、开发、测试、调试和部署 Eclipse 插件,帮助开发者在 Eclipse 工作台中完成插件开发的每个阶段。同时它提供了丰富的插件接口,可以允许插件扩展 Eclipse 用户界面,使这些用户界面带有菜单选择和工具栏按钮;请求不同类型事件的通知;以及创建新视图。

Eclipse 被设计成可以在多个操作系统上运行,提供与每个底层操作系统的强大集成。Eclipse 的插件可以作为可移植

的设计程序,在任何受支持的操作系统上不加改变地运行。

Eclipse 还提供了一组底层图形界面 API —— SWT(standard widget toolkit),它提供标准的外观,能够开发出高效率的 GUI 程序。

采用基于 Eclipse 平台的开发方式,能够充分利用 Eclipse 平台所提供的便利条件和丰富资源,使开发者可以专注于开发测试软件的核心功能,提高了开发的效率并加快了开发的进度。

#### 4 边界扫描软件设计开发

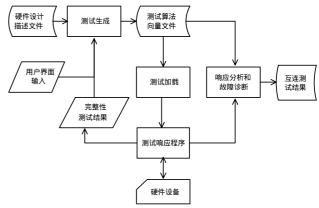

本软件系统主要由测试生成、测试向量加载及测试响应 分析和故障诊断等模块构成。软件总体设计架构如图 3 所示。

图 3 边界扫描软件架构

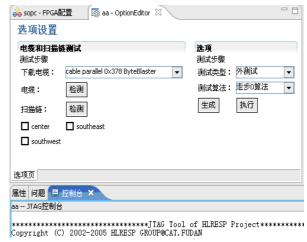

系统中与硬件直接交互的部分由 JTAG Tools 完成 ,它是一个开源的 CUI 软件包,通过一个 JTAG 适配器启用一起工作的 JTAG-aware (IEEE 1149.1)硬件设备和底板。用户界面采用 Eclipse 提供的 SWT 的 API 来实现。处理界面事件,生成硬件描述 XML 文件和算法矢量 XML 文件,分析和定位测试响应故障等主要功能全都由 Java 编码来完成。软件的用户界面设计如图 4 所示。

图 4 软件用户页面

## 4.1 测试生成

测试生成利用电路板的设计描述文件(如电路板的网表文件和器件的边界扫描描述语言文件等)获取被测对象的边界扫描链路及网络连接信息,依据一定的测试生成算法,生成边界扫描测试的向量集<sup>[4]</sup>。

电路板网络表文件描述板上各器件之间的互连关系。每个网络连接均由器件号与线路号加以描述,其格式在电子数据交换格式(EDIF)文件中有准确的规定。扫描器件连接描述

文件则描述了边界扫描链路的顺序和内容,从链路的 TDO 端上溯到 TDI 端,链路中每个器件需给出其在电路板上的名称、BSDL 文件等。本软件设计了一个 XML 格式文件,通过解析上述的描述文件自动生成,包含了实际被测的边界扫描链路以及网络连接信息等硬件配置信息,为互连测试提供了完整的信息。此 XML 文件格式定义示例如下:

```

<board id="jtag example" name="CAT Lab ">

<parts>//扫描链路器件的顺序和内容

<part id="center" type="EP1C6Q240" />

<part id="southeast" type="EPM7256AET144 />

<part id="southwest" type="EPM7256AET144 />

</parts>

<connects>//各器件之间的互连关系

<connect master="center" slave="southeast">

<signal master="IO103" slave="IO120"/>

<signal master="IO104" slave="IO117"/>

<connect master="center" slave="southwest">

<signal master="IO105" slave="IO121"/>

<signal master="IO107" slave="IO116"/>

</connect>

</connects>

</hoard>

```

HLRESP 样机由许多模块板组成,在构建样机时,有的模块板不一定安装。因此,系统的扫描链路需要可以动态配置,某块板子的缺省不能引起扫描链路不通。一般电路板的设计描述文件描述了扫描链中所有器件的顺序,但是在实际的测试中,可能没有安装某些器件,而导致完整性测试得到的边界扫描链路顺序和内容与提供的描述文件中的顺序和内容不完全吻合,如表1所示。

表 1 扫描链路比较

|               | 以太网 | 键盘 | Stratix | ARM |

|---------------|-----|----|---------|-----|

| 原提供的扫描链路顺序和内容 | 1   | 2  | 3       | 4   |

| 实际被测扫描链路顺序和内容 |     | 1  |         | 2   |

软件提供界面让用户选择哪些器件接入了扫描链路。这样,使完整性测试得到的器件描述能正确定位到电路板设计描述文件相应的器件上(如表 1 中,由于以太网和 Stratix 芯片没有安装,不在扫描链上,那么实际扫描链路上的第 2 块器件对应的是 ARM),并在执行互连测试过程中,忽略那些包含了不被测器件的互连网络(比如包含以太网或 Stratix 芯片的互连网络)。

不同测试算法的测试矢量集,测试运行的时间,以及故障定位能力都不一样。在实际运用中,需要根据待测网络数目进行灵活选取。本软件提供了各种测试算法选项,根据用户指定的算法,动态生成一个 XML 文件来存放产生的算法矢量,实际被测的互连网络,以及每个器件在扫描链中的顺序。此 XML 文件内容示例如下:

```

<br/>

```

</board>

#### 4.2 测试向量加载

测试向量加载模块的作用是把软件产生的测试数据加载 到被测对象中,控制被测对象进行测试,并得到测试对象的 响应数据。

JTAG Tools 提供了完整性测试。通过完整性测试,它为每个实际被检测到的器件指定一个索引号,此索引号代表了它在实际被测扫描链的位置。指定相应的索引号就可以选中相应的器件。但此软件包只提供对单个引脚加载和获取信号信息的功能,不能对多个引脚同时加载和获取信号信息。因此扩展了两条指令 setSignals 和 getSignals,实现了对整个器件所有引脚加载和获取信号的能力。测试向量加载的核心程序步骤如下:

```

//选中实际被测的扫描链上的第 n 块器件, 并把它设为驱动方

nart n

instruction EXTEST

//设置第 m 块器件为接受方

instruction SAMPLE/PRELOAD

//把这些器件的状态设置到位

shift ir

//测试向量加载开始

for(int i=0; i<测试向量组的总长度; i++){

//把向量作用到驱动方的引脚

part n

setSignals SIGNAL..SIGNAL VECTORS

//把数据作用到驱动方的 NDO

并把接受方的响应数据输出到 TDO

shift dr

shift dr

//从接受方的 TDO 得到响应数据并显示

getSignals SIGNAL ..SIGNAL

```

# 4.3 测试响应分析

根据返回的测试响应数据,诊断时,系统将读取的响应向量与测试矢量相比较,无须人工参与即可判断各个互连器件之间的连接关系是否正确。如果存在故障,能对故障进行准确的定位,为用户及时快速地排除故障带来方便。

#### 5 小结

在 HLRESP 样机平台的研制过程中,本测试软件方便了样机系统的调试、测试和维修工作,加快了样机平台的开发进程。本软件采用基于 Eclipse 插件的开发方式,是一个独立的、标准的 Eclipse 插件,因此,它也可以作为一个通用的测试软件,应用于其他具有标准边界扫描接口的系统的测试。

### 参考文献

- 1 宋克柱, 杨小军, 王砚方. 边界扫描测试的原理及应用设计[J]. 电子技术, 2001, (10).

- 2 Altera. IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices[Z]. 2006. http://www.altera.com/literature/an/an039. pdf, 2006

- 3 张学斌. 基于 JTAG 的互连测试技术[J]. 今日电子, 2004, (4).

- 4 游 方, 钱彦岭, 胡 政. 边界扫描测试仪软件系统开发[J]. 国防 科技大学学报, 2000, 22(3).