Vol.35

No.4 工程应用技术与实现。

文章编号: 1000-3428(2009)04-0244-03

文献标识码: A

中图分类号: TP333

February 2009

2009年2月

# 具有时间隐藏特性的数据块读写 SDRAM 控制器

王 斌,熊志辉,陈立栋,谭树人,张茂军

(国防科技大学信息系统与管理学院,长沙 410073)

摘 要:针对 SDRAM 控制器读写数据块访问延时长、速度慢的问题,提出时间隐藏技术,将其应用于 SDRAM 控制器的设计,采用 FPGA 实现。实验结果表明,时间隐藏技术有效缩短了数据块读写访问延时,提高了读写速度,写4×4数据块可节约时间52%,读8×8数据块 可节约时间 44%。

关键词:时间隐藏;数据块;SDRAM 控制器

# **SDRAM Controller with Time-hiding Feature** for Data Block Access

WANG Bin, XIONG Zhi-hui, CHEN Li-dong, TAN Shu-ren, ZHANG Mao-jun

(College of Information Systems and Management, National University of Defense Technology, Changsha 410073)

[Abstract] In order to speed up the efficiency of SDRAM controller while reading/writing data blocks, this paper proposes a time-hiding method for the design of SDRAM controller. It implements this method on FPGA. Experiments indicate that this time-hiding method shortens the latency and increases the speed of accessing data blocks. For example, when writing 4 x 4 data blocks, this method saves access time by 52%, and when reading 8 x 8 data blocks, this method saves access time by 44%.

Key words I time-hiding; data block; SDRAM controller

#### 1 概述

常用的 SDRAM 控制器在读写数据块时存在访问延时 大、读写速度慢的问题,难以满足数字媒体处理中快速读写 数据块的要求。为了降低 SDRAM 访问延时, 文献[1]提出了 Bank 交错控制,文献[2]提出使用 Bank 访问历史表指导预充 电策略,文献[3]提出通过 SDRAM 状态判断减少充电次数, 文献[4]提出数据写缓存和双通道预取指令缓冲器,文献[5] 提出命令寄存,以上策略和方法在一定程度上缩短了访问延 时。文献[6]针对 HDTV 应用中运动估计算法特点,采用相邻 宏块存储于不同 Bank 等方法提高 SDRAM 读写宏块速度。

文献[2]使用 Bank 访问历史表指导预充电,其算法较为 复杂,文献[3]减少了充电时间但读写过程中延时仍较大,文 献[4]在数据块较大时需要占用较多资源,文献[5]只缩短了命 令等待时间。本文提出时间隐藏技术,能够有效缩短数据块 读写访问延时,明显提高数据块读写速度。基本原理是:在 SDRAM 控制器读写时,同时运用交错 Bank 控制、命令寄存 和命令提前这3个策略达到时间隐藏的目的,从而缩短数据 块读写所需时间,提高读写速度。在 FPGA 平台上,设计并 实现了具有时间隐藏特性的数据块读写 SDRAM 控制器。实 验结果表明,与不具有时间隐藏特性的SDRAM控制器相比, 该控制器在读写数据块时能够有效节约时间,明显提高读写 速度,以写4×4数据块为例,节约时间可达52%,以读8× 8数据块为例,节约时间可达44%。

# 2 常用 SDRAM 控制器读写数据块的特点

常用 SDRAM 控制器一般把数据块存放在同一个 Bank 中,数据块内的一行对应于 Bank 中的一行。下面以读  $m \times n$ 数据块(数据位宽为 32 bit)为例分析常用 SDRAM 控制器读写

#### 数据块的特点,其流程如下:

(1)读第 0 行数据:在 READ 命令执行之前,必须通过 ACTIVE 命令把 Bank 中对应的 row 打开,从 ACTIVE 命令 有效到执行 READ 命令必须等待 tRCD 个周期,而 READ 命 令有效后还要等待 CL 个周期第 0 行数据才出现在数据总线 上。本文将从 ACTIVE 有效到数据总线上数据有效的时间称 为  $T_-bf_-d$ (Time before data), 将数据总线上数据有效时间称 为  $T_d$ v(Time of data valid),使用 MT48LC4M32B2-7 SDRAM 芯片,其数据位宽为 32 bit,数据有效时间  $T_{-}d_{-}v$  为 m 个周期。

(2)待第 0 行所有数据读出后,需要执行 PRECHARGE 命令关闭该 row 以便读第 1 行时可以打开对应的 row, 执行 PRECHARGE 命令需要 tRP 个周期。本文将数据读写完成到 关闭 row 的时间称为 T\_bh\_d(Time behind data)。

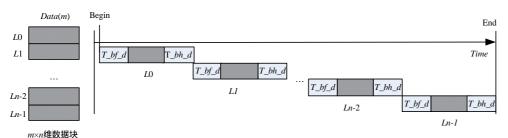

反复执行上述 2 步,直到完全读出  $m \times n$  数据块。图 1显示了常用 SDRAM 控制器读写  $m \times n$  数据块的时间关系。 从中可以得出常用控制器读写数据块的数据有效时间、读写 总时间、数据总线空闲时间的计算公式(以下公式只适用于 SDRAM 处于工作状态,不适用于非工作状态)。

#### 数据有效时间:

$T \_data \_valid = m \times n$ (1)

基金项目: 国家自然科学基金资助项目(60773023, 60705013); 中国 博士后科学基金资助项目(20070410977)

作者简介:王 斌(1983-),男,硕士研究生,主研方向:嵌入式系 统设计,数字媒体处理;熊志辉,讲师、博士;陈立栋,博士研究 生;谭树人,副教授、博士研究生;张茂军,博士、博士生导师

**收稿日期:** 2008-07-28 **E-mail:** nudtwangbing@163.com

#### 数据总线空闲时间:

$$T\_idle\_0 = (T\_bf\_d + T\_bh\_d) \times n$$

(2)

读写总时间:

$T_{total}_0 = (m + T_bf_d + T_bh_d) \times n$ (3)

图1 常用控制器读写m×n数据块的时间关系

下面采用 Micron 公司的 MT48LC4M32B2-7 SDRAM 芯片,以在带自充电模式下读写  $m \times n$  数据块为例,测试常用控制器的读写时间。实验中,时钟频率为 100 MHz, tRCD 为 3 个周期,tRP 为 2 个周期,CL 为 2 个周期,带自充电模式 tWR 为 2 个周期。

#### 读数据块时:

$T_bf_d = tRCD + CL = 5$ ,  $T_bh_d = tRP = 2$

#### 写数据块时:

$T_bf_d = tRCD = 3$ ,  $T_bh_d = tRP + tWR = 4$

在自充电模式下,读写 4×4 数据块(单位 32 bit)的总时间为 44 个周期,空闲时间为 28 个周期;读写 8×8 数据块(单位 32 bit)的总时间为 120 个周期,空闲时间为 56 个周期。可见,常用 SDRAM 控制器在读写数据块时,存在数据总线空闲时间较长、读写总时间长、读写速度慢的问题,难以满足数字媒体处理中快速读写数据块的要求。

从图 1 中可以看出,导致数据块读写效率低的主要原因是:读写一行数据时存在  $T_-bf_-d$  和  $T_-bh_-d$  时间。如果能够将 2 行数据之间的  $T_-bf_-d$ ,  $T_-bh_-d$  隐藏,就能减少数据总线空闲时间,缩短读写操作总时间,提高数据块读写速度。

#### 3 面向数据块读写的时间隐藏策略

#### 3.1 时间隐藏的原理

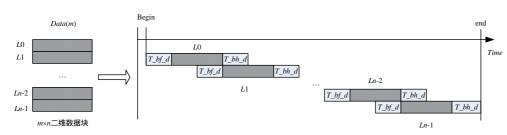

时间隐藏技术是通过一系列措施隐藏二维数据读写时的部分访问延时,缩短数据总线空闲时间,加快数据块读写速度。如图 2 所示,时间隐藏的基本原理是:在前一行数据尚未读写完成时,在适当的时刻提前启动后一行数据的读写操作,则后一行数据就能够在前一行数据读写完成后立即出现在数据总线上,使  $T_-bf_-d$ , $T_-bh_-d$  与数据有效时间  $T_-d_-v$  重叠,隐藏前一行的  $T_-bh_-d$  和当前行的  $T_-bf_-d$  时间,实现数据块内行与行之间的无间隔连续读写。

tRP 时间后才能激活该 Bank 中新的 row , 进行读写操作。因此,将数据块存储在同一个 Bank 中无法隐藏  $T_-bf_-d$  和  $T_-bh_-d$  时间。虽然 SDRAM 不支持在同一 Bank 中同时打开

多个 row , 但它支持同时打 开多个 Bank 的 row。因此 , 可以采用 Bank 交错控制和 命令提前 , 实现  $T_bf_d$  和  $T_bh_d$  时间隐藏 , 提高数 据块读写效率。

Bank 交错控制是指: 当一个 Bank 工作时,在恰 当的时机提前对另一个 Bank 进行预充电或者激活 和寻址(此时寻址的 Bank

是关闭的),当前一个 Bank 数据传输结束,下一个 Bank 的数据就立即出现在数据总线上,从而将 tRP, tRCD, CL(读)时间隐藏。常用 SDRAM 控制器还存在命令等待的问题,本文采取命令寄存的办法缩短命令等待时间。命令寄存是指:在"读、写、刷新"等命令执行条件尚不满足时,将其寄存,待条件满足再执行。命令提前策略:SDRAM 读写命令执行与数据传输可以在一定时间段内重叠,因此,可以在前一次读写命令已经执行但数据总线上数据仍在传输的情况下,以恰当时机提前执行新的读写命令,把命令执行时间隐藏于数据传输中,使前后 2 次读写数据无间隔地出现在数据总线上。时间隐藏技术就是通过 Bank 交叉控制、命令寄存、命令提前 3 个策略,隐藏数据块读写时行与行之间的 T\_bf\_d, T\_bh\_d 时间,缩短读写时间,提高数据块读写速度。

从图 2 中可以得出本文控制器读写数据块时的数据有效时间、读写总时间、数据总线空闲时间的计算公式(以下公式只适用于 SDRAM 处于工作状态,不适用于非工作状态)。

## 数据有效时间:

$$T_{data\_valid} = m \times n \tag{4}$$

数据总线空闲时间:

$$T_idle_1 = T_bf_d + T_bh_d$$

(5)

读写总时间:

$$T \_total \_1 = m \times n + T \_bf \_d + T \_bh \_d$$

(6)

比较式(2)和式(5)、式(3)和式(6)可发现:采用时间隐藏技术后,数据总线空闲时间缩短了  $(T_-bf_-d+T_-bh_-d)\times(n-1)$ 个周期,读写操作总时间也相应缩短了  $(T_-bf_-d+T_-bh_-d)\times(n-1)$ 个周期。因此,将时间隐藏技术应用于 SDRAM 控制器可以有效地缩短 SDRAM 控制器读写数据块所需时间,提高数据块读写速度。

图 2 时间隐藏原理

常用 SDRAM 控制器将数据块存储于同一个 Bank 中,同一个 Bank 只允许有一个 row 被激活,在新的读写操作之前,必须通过 PRECHARGE 命令关闭已经打开的 row,等待

#### 3.2 Bank 交错存储模式

为实现时间隐藏技术,需要改变常用控制器中数据块存储方式,采用 Bank 交错存储模式。Bank 交错存储模式是将数据存储于不同 Bank 中,数据块内第 n 行数据存储于第 m 个

Bank 中相应行,其中, m=n%4,即 m 为 n 除以 4 的余数。以 4 个 Bank 为例,  $m\times n$  数据块采用 Bank 交错存储模式的存储顺序是:数据块的第 0 行~第 3 行依次存放在第 0 个~第 3 个 Bank 某 row 中,第 4 行~第 7 行依次存放在第 0 个~

第3个Bank的下一row中,依此类推。

# 4 控制器的设计与实现

#### 4.1 控制器的总体结构

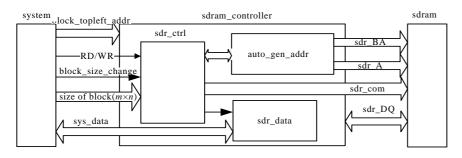

本文 SDRAM 控制器由 3 个主要功能模块:sdr\_ctrl, auto\_gen\_addr, sdr\_data 及其对外接口组成 具体如图 3 所示。

图 3 SDRAM 控制器原理

sdr\_ctrl 是主控制器,执行 system 的命令、产生 auto\_gen\_addr 和 sdr\_data 的控制信号、完成对 SDRAM 控制。auto\_gen\_addr 是地址自动生成模块,能够以数据块左上角(block\_topleft\_addr)坐标为基准,在主控制器控制下适时地自动生成数据块读写过程中各行数据在 SDRAM 中的 Bank, row, column 地址,可以避免常用控制器中频繁发送地址操作。sdr\_data 是数据路径,将读写数据送出或送入 SDRAM。

#### 4.2 控制器的逻辑设计

sdr\_ctrl 由刷新计数器(REF\_CNT)、RWL(Register\_Width\_Length)、控制状态机(Ctrl\_FSM)3部分组成。刷新计数器计数刷新时间,在控制状态机配合下产生刷新请求。RWL寄存数据块宽度和长度信息,分别作为读写数据块时宽度(width)和长度(length)的控制信号送入控制状态机中,控制SDRAM 按数据块大小读写数据块。

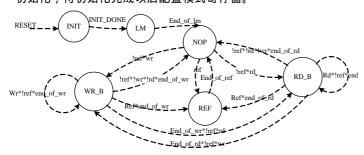

控制状态机需要完成 SDRAM 初始化、模式寄存器配置、数据块读写、SDRAM 刷新等任务,其简化的状态转移图如图 4 所示。当复位或上电以后,控制状态机进行 SDRAM 的初始化,待初始化完成以后配置模式寄存器。

图 4 状态机转移图

使用命令寄存技术将自刷新请求、读写等命令寄存后,需要有效的"仲裁机制"决定命令执行优先级。在"NOP"状态时,按照刷新请求优先级最高、读写命令先到先服务的原则执行;而在"WR\_B"和"RD\_B"状态时,如果读写完成且刷新请求有效,则转移到"REF"状态对 SDRAM 刷新,

否则,如果读写命令有效则进入相应的读写状态,无效则进入"NOP"等待新的命令。

## 5 实验结果

本文提出的控制器在 Xilinx 公司的 XS3C1000 芯片上实现,工作频率为 100 MHz,使用 340 个 Slices, 600 个 4 input

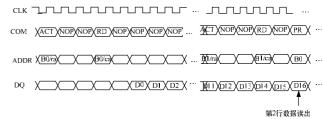

LUTs。图 5 是具有时间隐藏特性的数据块读写 SDRAM 控制器读  $16 \times 16$  数据块的时序图(CL=2),从中可以看出,数据块行与行之间的  $T_\_bf_\_d$ , $T_\_bh_\_d$  被隐藏,各行数据无间隔地从 SDRAM 中读出。与不具有时间隐藏特性的控制器相比,该控制器能够明显缩短读写数据块时间。以写  $4 \times 4$  数据块为例,节约时间可达 52%,以读  $8 \times 8$  数据块为例,节

约时间可达 44%。

图 5 读 16×16 数据块时序图

#### 6 结束语

本文融合交错 Bank 控制、读写命令寄存和命令提前 3 个策略,提出时间隐藏技术,应用于具有时间隐藏特性的 数据块读写 SDRAM 控制器设计,并在 FPGA 上实现。实验结果表明,与不具有时间隐藏特性 SDRAM 控制器相比,该控制器能够有效缩短数据块读写时间,明显提高数据块读写速度,满足数字媒体处理中对数据块快速读写要求。另外,本文提出的时间隐藏思想也适用于其他具有时间重叠特性的嵌入式系统。

#### 参考文献

- Lee K B. An Efficient Quality-aware Memory Controller for Multimedia Platform SoC[J]. IEEE Transactions on Circuits and Systems for Video Technology, 2005, 15(5): 620-633.

- [2] 李 文, 唐志敏. 一种减少内存访问延时的方法[J]. 计算机工程, 2006, 32(3): 242-244.

- [3] 刘 洋, 林争辉. 视频解码芯片中 DDR SDRAM 控制器的设计[J]. 计算机工程, 2006, 32(1): 240-242.

- [4] 张 宇, 时龙兴, 王学香, 等. 面向片上系统的高性能 SDRAM 控制器设计[J]. 固体电子学研究与进展, 2007, 27(3): 408-413.

- [5] 徐 红, 叶 丰, 孟利民. 基于图像处理的 SDRAM 常用接口设计[J]. 现代电子技术, 2006, (16): 67-69.

- [6] 赵 强, 罗 嵘, 汪 蕙, 等. 用于 HDTV 视频解码器的高性能 SDRAM 控制器[J]. 电子与信息学报, 2007, 29(6): 1332-1337.