## 新型 9/7 小波基构造及快速实现

王 前<sup>①②</sup> 吕东强<sup>③</sup> 栗 靖<sup>②</sup> 葛宝珊<sup>①</sup> (北京航空航天大学计算机学院 北京 100083) <sup>②</sup> (解放军 61081 部队 北京 100094) <sup>③</sup> (第二炮兵装备研究院四所 北京 100085)

摘 要: CDF9/7 小波的复杂系数是限制其快速实现的主要因素。该文构造了新的含参双正交提升小波模型,并利用能量集中性法则和迭代搜索算法提出一种压缩性能与此相当适合移位操作的有理数小波基。新小波基在硬件实现时可用一次移位和加法运算代替乘法运算,运算量仅为原来的 25%,且无需考虑位长对精度的影响。一维小波 4级流水架构已通过 FPGA 验证,与同类设计相比,减少一半的资源消耗量,并且大幅提高系统的工作频率。

关键词:小波变换;能量集中性;关键路径; JPEG2000; VLSI

中图分类号: TN47

文献标识码:A

文章编号: 1009-5896(2009)05-1210-04

# New Construction for 9/7 Wavelet Basis and Fast Implementation

Wang Qian  $^{\odot 2}$  Lü Dong-qiang  $^{\odot}$  Li Jing  $^{\odot}$  Ge Bao-shan  $^{\odot}$   $^{\odot}$  (School of Computer Science and Engineering, Beihang University, Beijing 100083, China)  $^{\odot}$  (61081 Army PLA, Beijing 100094, China)  $^{\odot}$  (The Fourth Institute of The Second Artillery Equipment Academy, Beijing 100085, China)

Abstract: Fast implementation of CDF9/7 wavelet is strictly retained for its complex coefficient. This paper constructs a new biorthogonal and lifting-based wavelet model with parameters. The new wavelet basis of rational number proposed is adapted to shift operation with the same compression performance to CDF9/7 by using energy concentration and iterative searching algorithm. One multiplication can be implemented by one addition and shift in the hardware design. It amounts to the original calculation quantity of 25% and its precision is not influenced by the word length. The 4 level pipelined architecture of one dimensional transform is demonstrated on the FPGA. Compared with the related design, it reduces half resource requirement and improves the working frequency of system prominently.

Key words: Wavelet transformation; Energy concentration; Critical path; JPEG2000; VLSI

## 1 引言

JPEG2000<sup>[1]</sup>是新一代的图像压缩标准,其核心算法是离散小波变换(DWT)和优化截断嵌入编码(EBCOT)。DWT 具有便于图像渐进式传输、能量集中性好等优点,在经过提升算法的改进后,与传统的卷积运算相比,可降低运算复杂度、减少存储需求,正逐步得到广泛应用。但运用提升算法的小波变换导致了更长的关键路径长度,不少学者对其硬件快速实现进行研究。文献[2]提出一种标准的 CDF9/7 小波流水线结构,文献[3]采用折叠方式实现小波变换,资源利用率达到 100%,但数据调度系统复杂。文献[4]建立了基于行变换的多级流水结构,并用定点法实现 17 位小波系数和 17 位滤波系数的乘积,虽然保证了数据精度,但需要大量的硬件

资源。上述研究大多集中在硬件结构的优化层次上,没有从 构造原理上对小波变换的实现进行优化改进。

本文在建立双正交提升小波构造模型的基础上,运用优化算法设计出一组适合硬件操作的优化小波基,并采用流水线和并行处理技术在 FPGA 芯片中进行优化实现。与同类结构相比,该结构具有资源消耗少、关键路径短等特点,特别适合应用在大数据量、强实时性的场合。

## 2 易于硬件实现的 9/7 小波基

在图像压缩中,CDF9/7 小波有着广泛的应用,其小波变换的能量集中性和恢复图像的 PSNR 值均有较好效果,已被 JPEG2000 所采纳。但其小波基系数均为无理数,硬件实现的成本较大。 文献[2]提出将无理数系数换算为 CSD (Canonical Signed Digit)形式,每个小波系数可减少 2 到 3 个加法的运算量。文献[5]通过滤波器对称特性降低小波系数的复杂度。文献[6]提出用二进制数代替浮点数进行小波变

<sup>2008-03-24</sup> 收到, 2008-07-07 改回

国家 863 计划项目(2006AA701121),教育部博士点基金和新世纪优秀人才支持计划资助课题。本研究在虚拟现实技术国家重点实验室完成

换,但未从硬件角度进行优化设计。本文将以 9/7 小波为基础采用优化算法构造适合硬件特点的双正交小波基,使之既能保持 CDF9/7 的优良压缩性能,又能确保硬件实现时的快速简便。

#### 2.1 双正交小波原理

根据双正交小波构造原理,设小波函数和对偶小波函数的长度分别为 9 和 7,考虑到双正交小波的中心对称性,可以分别用 5 个和 4 个未知数将其表示,分别记做  $\{h_n,0\le n\le 4\}$  和  $\{g_n,0\le n\le 3\}$ 。由双正交小波的完全重构条件可得

$$h_0 + 2\sum_{n=1}^{4} h_n = \sqrt{2}, \quad h_0 + 2\sum_{n=1}^{4} (-1)^n h_n = 0$$

(1)

同理, 由其对偶小波的完全重构条件可得

$$g_0 + 2\sum_{n=1}^{3} g_n = \sqrt{2}, \quad g_0 + 2\sum_{n=1}^{3} (-1)^n g_n = 0$$

(2)

另外由双正交小波和其对偶小波的双正交关系可得

$$g_0 h_0 + 2 \sum_{n=1}^{3} g_n h_n = 1, \quad \sum_{n=-1}^{4} g_{|n-2|} h_n = 0$$

$$\sum_{n=1}^{4} g_{(4-n)} h_n = 0, \qquad \sum_{n=3}^{4} g_{(6-n)} h_n = 0$$

(3)

联立式(2)、式(3)以及式(1)的第 1 个方程,令 g0、g1 为 参变量,通过消元、化简,最后可得其余 7 个未知数的双正 交 9/7 小波通解。

$$g_{2} = \frac{\sqrt{2}}{4} - \frac{1}{2}g_{0}, \quad g_{3} = \frac{\sqrt{2}}{4} - g_{1}$$

$$h_{0} = 2(h_{1} - h_{2} + h_{3} - h_{4})$$

$$h_{1} = \frac{g_{2}^{2}h_{2} + (g_{1}g_{2} - g_{0}g_{3})/2\sqrt{2}}{g_{1}g_{2} - g_{2}g_{3} - g_{0}g_{3}}$$

$$h_{2} = \frac{3\sqrt{2}/4 - g_{0}}{2 - 4\sqrt{2}g_{0}}$$

$$h_{3} = \frac{\sqrt{2}}{4} - h_{1}, \quad h_{4} = -\frac{g_{3}}{a}h_{3}$$

$$(4)$$

#### 2.2 优化小波基的产生

根据小波提升过程的基本原理,借助z变换和 Euclidean 因式分解法,分解9/7提升小波的矩阵表示可得式(5):

$$\begin{bmatrix} X_{l}(z) \\ X_{h}(z) \end{bmatrix} = \begin{bmatrix} \rho & 0 \\ 0 & 1/\rho \end{bmatrix} \begin{bmatrix} 1 & \delta(1+z^{-1}) \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ \gamma(1+z) & 1 \end{bmatrix}$$

$$\cdot \begin{bmatrix} 1 & \beta(1+z^{-1}) \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ \alpha(1+z) & 1 \end{bmatrix} \begin{bmatrix} X_{e}(z) \\ X_{o}(z) \end{bmatrix}$$

(5)

上式中 $X_e(z)$ , $X_o(z)$ 分别表示输入信号的偶奇部分, $X_l(z)$ , $X_h(z)$ 分别对应于滤波器的低通和高通输出。

9/7 小波提升分解的矩阵又可以表示为

其中 A 为  $h_0 + h_2(z + z^{-1}) + h_4(z^2 + z^{-2})$ , B 为  $g_1(1 + z^{-1})$

$+g_3(z+z^{-2})$  , C 为  $h_1(1+z)+h_3(z^{-1}+z^2)$  , D 为  $-g_0$   $-g_2(z^{-1}+z)$  。

联立式(5),式(6)可得式(7)

$$h_{0} = (1 + 2\alpha\beta + 2\alpha\delta + 6\alpha\beta\gamma\delta)\rho$$

$$h_{1} = (3\gamma\beta\delta + \beta + \delta)\rho$$

$$h_{2} = (\alpha\beta + \alpha\delta + \gamma\delta + 4\alpha\beta\gamma\delta)\rho$$

$$h_{3} = \beta\gamma\delta\rho, \quad h_{4} = \alpha\beta\gamma\delta\rho$$

$$g_{0} = (1 + 2\beta\gamma)\rho, \quad g_{1} = -(\alpha + \gamma + 3\alpha\beta\gamma)\rho$$

$$g_{2} = \beta\gamma/\rho, \quad g_{3} = -\alpha\beta\gamma/\rho$$

$$(7)$$

联立式(4),式(7)可得式(8)

$$\beta = -1/4(1+2\alpha)^{2}$$

$$\gamma = -1 - 4\alpha - 4\alpha^{2}/(1+4\alpha)$$

$$\delta = (4\alpha + 1)(8\alpha^{2} + 6\alpha + 3)/[2(4\alpha + 2)^{3}]$$

$$\rho = 2\sqrt{2}(1+2\alpha)/(1+4\alpha)$$

(8)

式(8)即为双正交提升9/7小波的通解,通过改变 $\alpha$ 的值,可以调整其余变量的值,即由变量 $\alpha$ 的值来确定小波系数。因此小波基的构造问题可以转化为以 $\alpha$ 为优化变量,压缩性能为目标函数,适合硬件实现为约束条件的变量优化问题。该优化问题的目标函数是一个多维曲面,在其值域范围内起伏变化无穷,无法用解析方法求解,需采用优化方法来对该问题进行求解。

如何定量地检验小波变换的压缩性能是一个很关键的问题。小波变换的正交性是变换前后能量不变的前提条件。由于 CDF9/7 小波是近似正交的双正交小波,所以图像经过 CDF9/7 变换后的频域能量近似等于空域能量。小波变换后 图像的能量集中到低频越多,高频能量就剩得越少,就越有利于压缩。因此本文以能量集中性作为标准来衡量新小波基的压缩性能。2.3 节也充分说明了这一结论的正确性。

假设一幅图像  $f_{i,j}, 1 \le i, j \le L$ ,其中 L 表示图像的长宽,经过小波变换后得到小波系数  $c_{i,j}, 1 \le i, j \le L$ , 其图像能量计算公式如下:

$$E = \sum f_{i,j}^2 \approx \sum c_{i,j}^2 \tag{9}$$

设图像经过小波变换后的各级频带能量按照从低到高的顺序记为 $E_i$ ,  $i=1,2,\cdots,5$ , 能量集中比例系数 $\eta_i=E_1/E_{\rm sum}$ , CDF9/7小波产生的 $\eta$  系数为 $\eta_L$ , 则 $\Delta\eta_i=\eta_L-\eta_i$ , 优化函数为 $f(\Delta\eta_i,\alpha_i,{\rm Pic}_m)$ , 其中 ${\rm Pic}_m$  为待处理的图像名称,因为不同的图像特征对压缩性能会产生影响,为保证实验的普适性,增加了一个变化变量 ${\rm Pic}_m$ 。

文献[7]指出  $g_0$  和  $g_1$  分别调整在CDF9/7系数的[-0.2,0.4] 与 [-0.1,0.3] 范围内,会取得比较好的效果。由此得到  $\alpha=-g_3/g_2=-(\sqrt{2}/4-g_1)/(\sqrt{2}/4-g_0/2)$  的取值范围为 [-3,-1]。硬件实现时,提升系数不能太长,这样可节省数据的存储代价,简化计算;同时尽可能使系数分母变为2的整数次幂,便于移位电路实现,减少运算误差。因此为提高搜索的效率和精度,本文提出"两步搜索"的策略。第1步

的"粗搜索"步长定义为  $\lambda_{\rm l}=2^{-1}$ ;在确定粗搜索的前提下, "细搜索"的步长定义为  $\lambda_{\rm 2}=2^{-5}$ 。在  $\alpha$  的变化范围内,从  $\alpha$  起始点开始,按照上述策略进行搜索,当前生成的最优变 量条件为  $\forall m \in [0,M], \{\alpha_i \mid \Delta\eta_i + \delta < \Delta\eta_i', {\rm Pic}_m\}$ ,其中  $\Delta\eta_i'$ 为上一次更新优化生成的  $\Delta\eta_i$ ,  $\delta$  为性能调节因子,本算法 确定为1/100。

优化算法的最终结果为  $\alpha=-1.5$ ,此时相关的小波提升系数为:  $(-3/2,-1/16,4/5,15/32,4\sqrt{2}/5)$ ,前 4 个为有理数,而且其中 3 个分母为 2 的幂,只有最后一个参数为无理数,统称为 compacted CDF9/7,简称 CCDF9/7。无理数  $\rho$  在多维变换时或在量化阶段统一转化为其平方数处理,减少了运算过程中的乘法运算冗余,消除了无理数的负面影响。因此本文暂时不考虑  $\rho$  的数值设置问题。从硬件实现的角度来看,这组系数无疑是较适宜的,但其压缩性能仍需要进行检测。

#### 2.3 性能测试

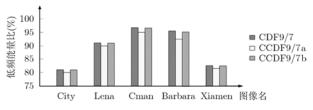

本节主要利用能量集中性和恢复图像 PSNR 值这两个指标验证新小波基在实际运用中的有效性。图 1 对比表示了新构造的小波基和 CDF9/7小波基对各类不同复杂度图像进行变换后的低频能量分布比例,低频即 LL 频带,小波变换级数统一定义为 5 级。为加强实验对比效果,本文增加了一组小波基 CCDF9/7a( $-1,-1/4,1/3,15/16,2\sqrt{2}/3$ )。对于不同的图像,由于其复杂程度的差异,低频能量比例也各有差异。图像越复杂,低频能量比例也越低。对于同一图像,与CDF9/7小波相比,新构造的小波基 CCDF9/7a 使得高频子带的能量明显增加,即该小波基的能量集中性差,而先前构造的 CCDF9/7b 能量集中性则与 CDF9/7 基本相当。

图 1 不同小波基的能量集中性对比图

表 1 是运用不同小波基进行 20 倍图像压缩后的结果。 实验平台为 P4 微机平台,CDF9/7 小波采用双精度数 (double 型),CCDF9/7 小波采用单精度数(float 型)。为准确评估小波基的压缩性能,本压缩算法中未引入位率优化控制模块。从中可以看出,在保持各自精度范围的情况下,经过 CCDF9/7b 和 CDF9/7 两种小波基压缩后的恢复图像 PSNR 值基本持平,而 CCDF9/7a 的压缩性能明显低于其他两种,故不予应用。在小波基硬件移植的过程中,嵌入式硬件系统的数据位宽更加有限,势必会影响数据精度。这样更能体现出新小波基位数短的优越性。上述两项实验结果充分说明了优化小波基 CCDF9/7b 在压缩性能方面的有效性。

表 1 构造小波基与 CDF9/7 小波基压缩效果对比(dB)

|         | CDF9/7 | CCDF9/7a | CCDF9/7b |

|---------|--------|----------|----------|

| City    | 21.84  | 21.46    | 21.83    |

| Lena    | 30.72  | 30.18    | 30.70    |

| Cman    | 28.52  | 27.78    | 28.51    |

| Barbara | 29.73  | 29.35    | 29.72    |

| Xiamen  | 21.09  | 20.40    | 21.06    |

接下来,本文依据新小波基系数,构造应用在 FPGA 上的 VLSI 模型。

### 3 VLSI 结构设计

如引言所述,一般采用流水线架构来设计小波变换。流水线的最大优势是能提高吞吐率,但这是以消耗硬件资源为代价的。提升小波可分为分裂、预测和更新3个步骤,根据其运算特点,同时为公平比较不同小波基硬件架构的性能,定义流水线级数为4级。

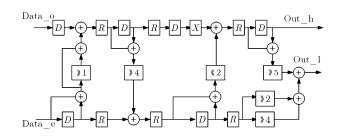

4 级流水架构的关键路径为 Tm+2Ta(Tm 代表乘法延时, Ta 代表加法延时)。若乘法运算被移位加代替,考虑到运算精度的影响,无理数通常需要较多的位数表示,位数越多,精度越高。由于受到硬件位宽的限制,需要在精度和资源耗费间进行折中。硬件位宽一般定义为 16 位,前两位是符号位和整数位,则小数部分的位宽为 14 位,结合具体的CDF9/7 小波系数,小波部分的实际有效位为 8 位。这样 Tm等价为 Ts+7Ta。而新小波基 CCDF9/7b 由于均是有理数,需要的位长较短,则 Tm 可等价为 Ts+Ta(Ts 代表移位延时)。运算量由 7 次移位、9 次加法变为 1 次移位、3 次加法,只占原先的 25%。详细的硬件结构图见图 2。

图 2 基于 CCDF9/7b 的一维小波变换图

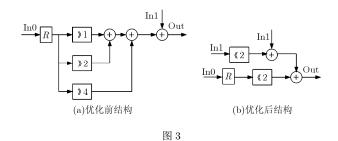

系数中有一个分母为 5,不是 2 的整次幂,可利用并行和数学代换的原理,把分母转换为乘法,此乘法可通过左移操作实现,这样可以把移位和多次加法的串行复杂运算分解成移位和乘法的并行运算,提高执行效率,并减少了精度误差。改进前后的结构对比图如图 3 所示。图 3(a)结构中尽管经过多次移位和加法,但精度误差仍有 0.0125,若要改善这一精度,势必需要消耗更多的硬件资源,并带来更长的路径延时。图 3(b)结构并没有引进多余的误差。为保证最终结果的正确输出,归一化系数 ρ 要作相应的变化处理。

## 4 实验结果及性能分析

为验证所提结构的有效性,本文采用 verilog 语言设计了 3 种不同方式的一维小波结构,并在 Virtex4 型的 FPGA 芯片上进行对比实验。编译软件为 XilinxISE7.1,仿真软件为 Modelsim5.8。具体的实验结果如表 2 所示。

表 2 小波实现结构的综合结果

| 实现<br>结构        | Slice | DSP | 输出<br>时延 | 吞吐<br>率<br>(B/s) | 最高<br>频率<br>(MHz) | 关键<br>路径  |

|-----------------|-------|-----|----------|------------------|-------------------|-----------|

| CDF9/7<br>(4 级) | 392   | 0   | 4T       | 194              | 97                | Ts+9Ta    |

| CDF9/7<br>(全流水) | 202   | 12  | 12T      | 500              | 250               | ${ m Tm}$ |

| 本文<br>(4级)      | 179   | 0   | 4T       | 284              | 142               | Ts+3Ta    |

结构 1 和结构 3 的操作流程基本相同,结构 3 的小波基系数均为有理数,并且利用了并行均衡技术,减少了运算次数和寄存器的个数,因此得到较高的性能。结构 2 中乘加运算利用 FPGA 中的 DSP 模块实现,同时为缩短关键路径,在每个运算单元之间添加了寄存器,得到的工作频率为250MHz,但耗费的资源代价也是 3 种结构中最大的。综合来看,本文所提的结构在性能代价比上具有很大的优势。此外,本文结构在 Virtex-II XC2V2000 芯片上也进行仿真实验,最高工作频率达到91MHz,吞吐率为182MB/s,远高与文献[8]提出的每秒钟40M 像素的处理量。文献[4]的提升小波结构在 FPGA 芯片上的工作频率为115MHz,在0.35µm ASIC 工艺下的频率也仅为150MHz,因此其性能稍逊于本文。

## 5 结束语

本文在建立双正交提升 9/7 小波通用模型的基础上,使用优化方法,设计出简单的有理数小波基。该小波基能量集中性强,压缩性能与传统 CDF9/7 基本相当。根据该小波基

的系数特点,结合 FPGA 芯片资源特性,利用流水和并行均 衡技术,设计了一种适合硬件实现的小波变换 VLSI 结构, 具有资源利用率高、吞吐能力强等优势,可开发成独立的 IP 核广泛应用在图像压缩的编解码芯片中。

## 参考文献

- [2] Lian C J and Chen K F. Lifting based discrete wavelet transform architecture for JPEG2000. Proceedings of the 2001 IEEE International Symposium on Circuits and Systems, Piscataway, 2001: 445–448.

- [3] Andra K, Chakrabarti C, and Acharya T. A VLSI architecture for lifting-based forward and inverse wavelet transform. *IEEE Trans. on Signal Processing*, 2002, 50(4): 966–977.

- [4] Seo Y H and Kim D W. VLSI architecture of line-based lifting wavelet transform for motion JPEG2000. IEEE Journal of Solid-State Circuits, 2007, 42(2): 431–440.

- [5] Martina M and Masera G. Low-complexity, efficient 9/7 wavelet filters VLSI implementation. *IEEE Trans. on Circuits and Systems-II: Express Briefs*, 2006, 53(11): 1289–1293.

- [6] Zhong Guangjun, Cheng Lizhi, and Chen Huowang. A simple 9/7-tap wavelet filter based on lifting scheme. Proceedings of the 2001 IEEE International Conference on Image Processing, Thessaloniki, Greece, 2001, 2: 249-252.

- [7] Li Bo, Jiao Runhai, and Li Yuancheng. Fast adaptive wavelet for remote sensing image compression. *Journal of Computer Science & Technology*, 2007, 22(5): 770–778.

- [8] 朱珂,华林,鲁则瑜.应用于 JPEG2000 的高性能离散小波变换 VLSI 结构.计算机辅助设计与图形学学报,2004,16(7):1010-1015.

- Zhu Ke, Hua Lin, and Lu Ze-yu. High performance VLSI architecture of discrete wavelet transformation for JPEG2000[J]. *Journal of Computer Aided Design & Computer Graphics*, 2004, 16(7): 1010–1015.

- 王 前: 男,1978年生,工程师,研究方向为图像压缩技术及其硬件实现.

- 吕东强: 男,1978年生,工程师,研究方向为图像压缩及融合技术.

- 栗 靖: 女,1969年生,工程师,研究方向为多媒体技术、智能信息处理.

- 葛宝珊: 男,1967年生,副教授,研究方向为数字视频处理、计算机网络和嵌入式系统.