# EXPERIMENTAL STUDIES OF NEW GaAs METAL/INSULATOR/p-n<sup>+</sup> SWITCHES USING LOW TEMPERATURE OXIDE

## K. F. YARN\*

Far East College, Department of Electrical Engineering, Optoelectronic Semiconductor Center, Hsin-Shih Tainan, Taiwan 744, Republic of China

(Received 17 December 2001; In final form 21 March 2002)

First observation of switching behavior is reported in GaAs metal-insulator-p-n<sup>+</sup> structure, where the thin insulator is grown at low temperature by a liquid phase chemical-enhanced oxide (LPECO) with a thickness of 100Å. A significant S-shaped negative differential resistance (NDR) is shown to occur that originates from the regenerative feedback in a tunnel metal/insulator/semiconductor (MIS) interface and p-n<sup>+</sup> junction. The influence of epitaxial doping concentration on the switching and holding voltages is investigated. The switching voltages are found to be decreased when increasing the epitaxial doping concentration, while the holding voltages are almost kept constant. A high turn-off/turn-on resistance ratio up to  $10^5$  has been obtained.

Keywords: Negative differential resistance (NDR); Liquid phase chemical-enhanced oxide (LPECO)

## **1 INTRODUCTION**

NDR switching behaviors have been observed in metal-insulator- $n-p^+$  or metal-insulator- $p-n^+$  structures [1, 2] and a theory has been published [3, 4] which attributes this switching property to either by deep-depletion region extending to the  $p-n^+$  region (punch-through mode) or by avalanching in the  $p-n^+$  region (avalanche mode). The presence of NDR characteristics plays a predominant role on the fabrication of high speed shift register [5], gas detector [6] and logic circuit [7].

Over the past years, effects have been made in pursuit of growing high quality, stable and low temperature GaAs oxide for metal/oxide/semiconductor (MOS) device applications, such as using condensed gases [8], laser beams [9], optical illumination [10], electric potential [11] or excited plasma [12]. However, these chemical reaction methods make the oxidation process become more complicated. In this work, we propose the LPECO [13] process to grow oxide in the GaAs MIS switch (MISS) at low temperature. In addition, to examine the effect of the doping concentration of the epitaxial layer on the switching and holding voltages, four different wafers are grown and investigated. From experimental results, the superiority of LPECO method demonstrates the ease of oxidation over conventional technique

<sup>\*</sup> Present address: P.O. BOX 345, Tainan, Taiwan 704, Republic of China.

ISSN 0882-7516 print; ISSN 1563-5031 online © 2002 Taylor & Francis Ltd DOI: 10.1080/0882751021000012535

and the high performance of oxide film quality. Due to the idea of using LPCEO, a conceptual understanding of such a set of results would enhance our understanding of the physics of MIS switching devices and oxide-based III–V semiconductor [14] devices in general.

#### 2 EXPERIMENTAL

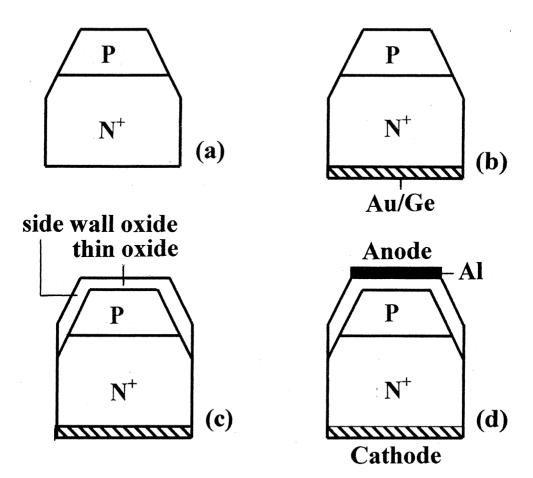

The studied GaAs MIS switching device was grown by AIXTRON 2400 metalorganic chemical vapor deposition (MOCVD) system on a (100)-oriented n<sup>+</sup>-GaAs substrate. Trimethylgallium (TMGa) and tertiarybutylarsenic (TBAs) were used as GaAs sources. The epilayers consisted of a 0.1 µm-thick n<sup>+</sup>-GaAs ( $n = 5 \times 10^{18}$  cm<sup>-3</sup>) buffer and a 0.5 µm-thick p-GaAs as shown in Figure 1(a). There were four different p-type doping levels,  $5 \times 10^{16}$  cm<sup>-3</sup>,  $8 \times 10^{16}$  cm<sup>-3</sup>,  $1 \times 10^{17}$  cm<sup>-3</sup> and  $4 \times 10^{17}$  cm<sup>-3</sup>, were used as parameters to investigate the doping effects on the variations of electrical properties. The epitaxial doping concentrations and thicknesses were measured by the electrical capacitance-voltage (ECV) instrument. The dopants used for the n and p layers were disilance (Si<sub>2</sub>H<sub>6</sub>) and dimethylzinc (DMZn), respectively. After the epitaxial growth, the structure was isolated by using H<sub>2</sub>SO<sub>4</sub>:8H<sub>2</sub>O<sub>2</sub>: 100H<sub>2</sub>O etching solution as shown in Figure 1(a). Au/Ge was deposited by evaporation

FIGURE 1 The process flow diagrams of the GaAs MISS by LPECO technique (a) mesa etching; (b) cathode ohmic contact; (c) low temperature oxidation; (d) anode schottky metal.

for the cathode ohmic contact as shown in Figure 1(b). Then, the GaAs wafer was only immersed into the gallium-ion-contained nitric acid solution to form the thin oxide on GaAs surface and side-wall oxide as shown in Figure 1(c). At an oxidation temperature of 40 °C for 30 minutes, the thickness of the oxide film on p layer is about 100Å. Finally, an Al non-alloyed contact deposition and lift-off process was employed to develop the anode contact as shown in Figure 1(d). The anode size is  $20 \,\mu\text{m} \times 20 \,\mu\text{m}$ . The DC current–voltage (*I–V*) characteristics of the studied device were measured at room temperature by a Tektronix 370A curve tracer and an HP 4145B parameter analyzer.

### **3 RESULTS AND DISCUSSION**

The regenerative feedback of bi-stable MISS devices is dependent on the  $pn^+$  junction and a MIS diode.[3, 4] When biasing the anode (A) positively to the cathode (K), no inversion is formed at insulator interface and a deep depletion occurs. This is the high impedance "off" state. In this case, the thin insulator just allows a small leakage current across the MISS device. If the applied voltage ( $V_{AK}$ ) is increased further, an injection current due to the electron minority carriers appears at the metal semiconductor (MS) interface, which the insulator can not allow to go through and accumulates at the interface. The accumulated electrons across the oxide cause a flow of holes in the other direction. These holes flow across the  $pn^+$  junction and induce a further flow of electrons from  $n^+$  to the oxide. Finally, a charged inversion layer forms and the wide depletion layer collapses. This is the low impedance "on" state. The voltage across the device is drastically reduced and the final holding voltage ( $V_H$ ) is almost due to the voltage drop in the  $p-n^+$  junction and metal-insulator interface.

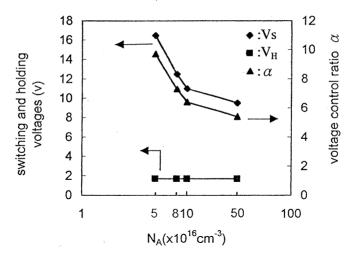

Figure 2(a) and (b) show the experimental I–V curves, measured by a Tektronix 370A curve tracer, of the LPCEO-grown MISS with p-type doping concentration of  $5 \times 10^{16}$  cm<sup>-3</sup> and  $8 \times 10^{16}$  cm<sup>-3</sup> at 300 K. As we expected, once the applied voltage (V<sub>AK</sub>) is not so large, the conducting current is too small to be evaluated. If the V<sub>AK</sub> voltage is increased to the value of V<sub>s</sub>, an interesting S-shaped NDR performance is observed in the I–V characteristic. The corresponding V<sub>s</sub> and V<sub>H</sub> are 16.5 V and 1.7 V shown in Figure 2(a) for p-type doping concentration of  $5 \times 10^{16}$  cm<sup>-3</sup>, while the corresponding values shown in Figure 2(b) for doping concentration of  $8 \times 10^{16}$  cm<sup>-3</sup> are 13.0 V and 1.7 V, respectively Experimental holding voltages, V<sub>H</sub>, are almost kept 1.7 V in the final on state. For example, a significant voltage control ratio ( $\alpha$ ) V<sub>S</sub>/V<sub>H</sub> of 9.7 has been obtained in Figure 2(a) and may have good potential for switching applications. The V<sub>s</sub>, V<sub>H</sub> and  $\alpha$  at the four different concentrations of each wafer are measured, and the results are shown in Figure 3. It is observed that the V<sub>s</sub> decreases with increasing N<sub>A</sub> and that the trend of V<sub>s</sub> is in agreement with the avalanche mode [3] in relatively high doping epilayers. Typical logI<sub>AK</sub> against V<sub>AK</sub> characteristics for the MISS also have been measured by a computer-controlled HP 4145B. The dynamic resistance, *r*, is defined as

$$r = n \mathrm{KT} / \mathrm{qI}_{\mathrm{AK}}$$

where  $n=(q/KT)(dV_{AK}/d\ln J_{AK})$ .

Consequently, the typical dynamic turn-on and turn-off resistances are  $20 \Omega$  and  $2 M \Omega$ , respectively. Compared to the conventional MIS structures, the LPCEO method [14] exhibits not only the ease and low temperature of growing GaAs oxide but also the passivation of insulated side-wall oxide at the same time.

FIGURE 2 The typical *I–V* characteristics of the GaAs MISS with different epitaxial doping concentrations of (a)  $N_A = 5 \times 10^{16} \text{ cm}^{-3}$  (b)  $N_A = 8 \times 10^{16} \text{ cm}^{-3}$ .

FIGURE 3 The switching voltages, holding voltages and voltage control ratios as a function of epitaxial doping concentrations. The switching voltages and voltage control ratios decrease with increasing doping concentrations.

## 4 CONCLUSIONS

We have investigated the electrical properties of GaAs Al/insulator/p-n<sup>+</sup> MIS switches prepared by MOCVD with an LPCEO-grown low temperature (40 °C) oxide as the insulator for the first time. The switching voltages, holding voltages and voltage control ratios at four different epitaxial doping levels are measured. It is observed that the switching voltages and voltage control ratios decrease with increasing doping concentration, while the holding voltages keep constant. The LPCEO method can provide a reliable oxide and reduce the lithography process in oxide-based III–V semiconductor devices. High on/off voltage control ratio of 9.7 and resistance ratio of  $10^5$  also have been obtained. These imply that the SCR-like switch has good immunity from environmental noise and may offer considerable potential in MOS compatible circuit and switching oscillation applications.

### Acknowledgement

This work is partially supported by National Science Council of the Republic of China under contracts No. NSC-89-2215-E006-006 and NSC-89-2219-E006-012

#### References

- [1] Yamamoto, T. and Morimoto, M. (1972). Appl. Phys. Lett., 20, 269.

- [2] Kroger, H. and Wegener, H. A. R. (1977). Solid-State Electron., 21, 643.

- [3] Simmons, J. G. and El-Badry, A. (1977). Solid-State Electron., 20, 955.

- [4] Habib, S. E. D. and Simmons, J. G. (1978). Solid-State Electron., 22, 181.

- [5] Yamamoto, T. and Kawamura, K. (1976). Solid-State Electron., 19, 701.

- [6] Kawamura, K. and Yamamoto, T. (1983). IEEE Electron Device Lett., EDL-4, 88.

- [7] Darwish, M. M. and Board, K. (1978). Electron. Lett., 14, 482.

- [8] Basu, N. and Bhat, K. N. (1988). J. Appl. Phys., 63, 5500.

- [9] Wilmsen, C. W., Kirchner, P. D., Baker, J. M., McInturff, D. T., Pettit, G. D. and Wooldall, J. M. (1988). J. Vac. Sci. and Technol. B, 6, 1180.

- [10] Ettedgui, E., Park, K. T., Cao, J., Gao, Y and Ruckman, M. W. (1995). J. Appl. Phys., 77, 5411.

- [11] Schmuki, P., Sproule, G. I., Bardwell, J. A., Lu, Z. H. and Graham, M. J. (1996). J. Appl. Phys., 79, 7303.

- [12] Nakamura, R. and Ikoma, H. (1996). Jpn. J. Appl. Phys., 35, L8.

- [13] Wang, H. H., Huang, C. J., Wang, Y. H. and Houng, M. H. (1998). Jpn. J. Appl. Phys., 37, L67.

- [14] Wu, J. Y, Wang, Y. H. and Houng, M. H. (1999). IEEE Electron Device Lett., 20, 18.