# 微型 SAR 的数字下变频设计

王虹现 李 刚 邢孟道 张守宏 (西安电子科技大学雷达信号处理重点实验室 西安 710071)

摘 要:在微型 SAR 实时成像样机的设计中,对雷达回波在中频进行采样,然后采用数字下变频技术实现正交解调,可以减少系统的复杂性,提高雷达的数字化程度和性能。该文针对微型 SAR 方案中数字下变频设计中的难点,即采样频率高达 2 Gsps,带宽 900 MHz,实时处理的难度很大,根据具体设计参数优化了数字下变频的实现结构,重点比较了并行 FIR 滤波器和快行 FIR 滤波器的差别,然后在 FPGA 中编程实现了数字下变频模块,给出资源占用情况、运行速度和量化噪声影响,最后给出在微型 SAR 技术项目中的实际应用结果,理想的成像结果表明了该设计的正确性。

关键词: 合成孔径雷达(SAR); 数字下变频(DDC); 模数转换(AD); FPGA

中图分类号: TN957.5 文献标识码: A 文章编号: 1009-5896(2010)02-0485-05

**DOI**: 10.3724/SP.J.1146.2008.01770

## Design of Digital Down Converter of Mini SAR

Wang Hong-xian Li Gang Xing Meng-dao Zhang Shou-hong (National Key Lab. of Radar Signal Processing, Xidian Univ., Xi'an 710071, China)

Abstract: In the designation of the real-time imaging machine of Mini SAR, the radar return signal is sampled in the intermediate frequency, then Digital Down Converter(DDC) is used to realize quadrature demodulate, which can reduce system complexity and improve radar's performance. The difficulty in the design of the DDC of Mini SAR is firstly given in this paper, i.e. the sampling frequency is as high as 2Gsps and the bandwidth is 900MHz, which leads large difficulty in real-time processing. The optimal architecture of DDC based on real design parameters is given in the next, with the emphasis on the difference of the parallel FIR filter and fast FIR filter. Then the implementation of the DDC module using parallel processing with optimized structure in FPGA is given, the resource usage, running speed and quantity noise influence are given. Finally, the result of Mini SAR is given, which confirms the validity of the design.

Key words: Synthetic Aperture Radar (SAR); Digital Down Converter (DDC); Analog to Digital (AD); FPGA

### 1 引言

现代战争需要对战场态势的即时掌握,合成孔径雷达(SAR)能得到地面的高分辨图像,并且不惧各种恶劣天气如大雾、大雨、沙尘暴和云层,不受白天和黑夜的影响,具有很大的作用距离,可以大大提高雷达的信息获取能力,已成为战场侦察的主要手段。微型系统将有助于减少对载体的空间和负荷的需求,有利于增加载体的机动性、灵活性和续航能力。同时微型系统也将扩展 SAR 的使用范围,使得具有该功能的传感器可以装在更小、更灵活和更为廉价的无人飞行器,小型卫星上,或者装在全天候精确制导武器上以便对目标进行精确打击,军事和民用前景广阔。

微型 SAR 要求的分辨率较高,发射信号的带宽达到 900 MHz,可以采用模拟方法进行正交解调后

得到基带信号,然后使用双路 1 Gsps 的采样速率进 行采样。然而由于集成电路发展迅速,高速 AD 芯 片和高性能 FPGA 芯片的出现,例如高速 AD 芯片 速度已经达到 2 Gsps、3 Gsps 甚至 5 Gsps, 高性能 FPGA 芯片的速度和规模都逐年提高,使得可以使 用单路2Gsps的采样速率对模拟信号进行直接中频 采样。直接中频采样在中频而不是在基带对模拟信 号进行采样,省去模拟的正交解调环节,使用单路 2 Gsps 的采样速率代替双路 1 Gsps 的采样速率,可 以减少系统的复杂性,提高整个雷达的数字化程度, 提高性能,增强可编程性和灵活性。采用直接数字 下变频技术得到数字正交双路信号,其正交性和一 致性要远远好于传统模拟方法得到的正交双路信 号。现在高采样率的 AD 器件已经十分成熟,专用 的 DDC 芯片适用的采样频率较低。文献[1-7]采样 速度都没有达到 2 Gsps, 文献[5]可实现任意中频, 文献[6]适用于抽取率较大的情况,文献[7]使用多个

AD芯片进行采样然后分别进行 DDC 来实现以达到较高的信噪比,所以本文主要研究使用高性能FPGA 芯片来实现数字下变频。

本文首先给出数字下变频的设计参数;随后给出数字下变频的实现结构;接着对数字下变频的核心部分即 FIR 滤波器的实现结构进行比较;然后在FPGA 中编程实现整个处理流程,给出运行速度和资源占用情况,并给出实现过程中的量化误差;最后给出具体的应用结果。

#### 2 设计参数

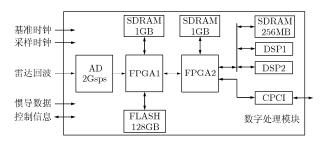

该微型 SAR 实时成像样机工作于 X 波段,中心频率为 10 GHz,发射线性调频信号的带宽为 900 MHz,发射信号的脉冲宽度为 7 μs,地面条带宽度大于 1500 m,距离向采样时间为 16 μs。我们对数字处理部分进行高度集成,由一块板卡完成对雷达回波的采样、存储以及实时成像处理,该微型 SAR实时成像样机的数字处理部分硬件结构图如图 1 所示。

图 1 数字处理部分硬件结构图

图中高速 AD 的采样速率为 2 Gsps,采样位数为 10 bit。高速大容量存储部分由 FLASH 阵列组成,通过 64 片 FLASH 芯片并行操作,可以实现 300 MB/s 的稳定连续写速度,存储容量为 128 GB。两片高性能的 FPGA 是整个板卡的核心,负责数据流的控制和实时成像算法的实现,每片 FPGA 都自带 1 GB 的 DDRII SDRAM。DSP 为 AD 公司的TS201,两片 DSP 共享容量 256 MB 的 SDRAM,DSP 之间采用 LINK 口互连实现高速数据通信。

雷达回波经低噪声放大器后进行下变频,中频频率为 1.5 GHz,信号带宽为 900 MHz,首先由高速 AD 部分完成对雷达回波中频信号的模数转换,然后将数据传送给 FPGA1,由 FPGA1 完成对回波信号的数字正交下变频、多普勒中心校正、方位向预滤波和成像处理中的距离压缩,然后将距离压缩后的数据传送给 FPGA2 和 DSP,由 DSP 完成参数估计,由 FPGA2 完成运动补偿和方位压缩,得出实时的图像。同时任何部分的数据以及最后的图像

结果都可以存储在 FLASH 存储部分。

在该微型 SAR 实时成像样机的数字下变频设计中,主要的难点就是采样速度太高,达到 2 Gsps,而 FPGA 内部的时钟速度一般在 300 MHz 左右。有两种办法来处理这么高速率的数据,一是在数字下变频模块前面加上缓冲,降低输入数据的速度,这种方法需要缓冲一个距离向的数据,需要 256 kb的存储器,但是这种方法有一个限制,就是方位向的重复频率不能太高,否则因缓冲导致的速度降低效果有限,不能达到 FPGA 中运行的 300 MHz 左右。本文采用并行处理技术,通过提高数字下变频的吞吐率,即在一个时钟周期内处理 8 个输入数据,让 FPGA 内部的时钟运行在 250 MHz,完成数字下变频的处理,该方法无需在前面加缓冲,能够达到实时处理的要求,而且使用资源较少。

## 3 数字下变频的实现结构

直接中频采样遵循带通采样定理,要求采样频率  $F_s$  大于信号带宽 B 的 2 倍,即  $F_s \ge 2B$ ;信号的中心频率  $F_0$  等于信号采样频率  $F_s$  的 1/4 的奇数倍,即  $F_0 = (2n-1) \cdot F_s / 4$ ,n 取为正整数。

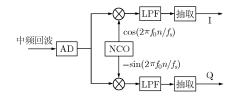

直接中频采样后需要进行数字下变频以得到基带信号,数字下变频的常见方法有低通滤波法凹、希尔伯特变换法凹、贝塞尔插值法间以及多相滤波法凹,这些方法本质上都可以归结为低通滤波器的设计。低通滤波法的结构与传统模拟处理方法有相似之处,只是将移频放在 A/D 变换之后。希尔伯特变换法和插值法都是只对一路通道进行滤波,另一路通道则保留了原来的采样值。任何一种方法,I/Q 两路幅度一致性和正交性取决于所采用滤波器的理想程度,要求越高,则需要的滤波器级数越多,实现起来越复杂。本文采用低通滤波法进行设计,其实现框图如图 2 所示。

图 2 低通滤波法结构

本设计中,中频频率为 1.5 GHz,采样频率为 2 GHz,即  $F_0 = 3 \cdot F_s / 4$ ,则

$$\begin{aligned} \cos(2\pi F_0 \cdot n / F_s) &= \cos(3\pi / 2 \cdot n) \\ &= 1, 0, -1, 0, 1, 0, -1, 0, \cdots \\ -\sin(2\pi F_0 \cdot n / F_s) &= -\sin(3\pi / 2 \cdot n) \\ &= 0, 1, 0, -1, 0, 1, 0, -1, \cdots \end{aligned} \tag{1}$$

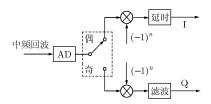

与输入的数据相乘后, I 路的奇数部分都为零, 只余下偶数部分, Q 路的偶数部分都为零, 只余下奇数部分, 这时可以将抽取提前, 相当于将输入数据的偶数部分送给 I 路, 将输入数据的奇数部分送给 Q 路, 原来 I 路的低通滤波器只剩下偶数部分, Q 路的低通滤波器只剩下奇数部分。由于设计的低通滤波器是一个半波带滤波器, 其偶系数(中心抽头除外)都为零, 所以 I 路的低通滤波器只剩下中心抽头处的一个系数, 通过延时就可以实现 I 路的滤波, 简化后的实现结构如图 3 所示, 与插值法的实现结构相同。

图 3 低通滤波法简化结构

根据微型 SAR 系统参数,采样频率为 2 GHz, 在与 AD 接口处的数据接收部分,使用 LVDS 接口模块自动将数据分成 8 路并行输入,每路数据的输入速度为 250 MHz,其中 4 路属于偶数序列,直接送给 I 路,另外 4 路属于奇数序列,直接送给 Q 路。上图中混频相乘部分可以通过简单的取反电路来实现,经过混频部分后,I 路和 Q 路都是有 4 路数据同时输入,I 路延时部分的并行处理直接对 4 路数据同时输入,I 路延时部分的并行处理直接对 4 路数据分别进行延时就可以实现,使用 FIFO 或者寄存器都可以实现,而 Q 路的滤波就需要设计一个同时能够接收 4 个数据输入和 4 个数据输出的并行滤波器。所以数字下变频实现的重点就是 Q 路的并行 FIR 滤波器的设计,该 FIR 滤波器并行度为 4,工作频率可以达到 250 MHz,其系数为原低通滤波器的奇数部分。

#### 4 快行 FIR 滤波器结构

假设一个 FIR 滤波器 [8] 的系数为 h(n),输入为 x(n),输出为 y(n),则有以下关系:

$$y(n) = x(n) \otimes h(n) \tag{3}$$

变换到 Z 域有以下关系:

$$Y(z) = X(z) \cdot H(z) \tag{4}$$

对式(4)进行 2 相分解,可得到式(5)和式(6)两种形式:

$$Y_0 = X_0 H_0 + z^{-1} X_1 H_1$$

$$Y_1 = X_0 H_1 + X_1 H_0$$

(5)

$$Y_0 = X_0(H_0 - H_1) + (X_0 + z^{-1}X_1)H_1$$

$$Y_1 = -X_0(H_0 - H_1) + (X_0 + X_1)H_0$$

(6)

按式(5)对式(4)做 4 相分解,则可分别求得 $Y_0$ ,  $Y_1$ ,  $Y_2$ 和 $Y_3$ :

$$Y_{0} = X_{0}H_{0} + z^{-1}X_{1}H_{3} + z^{-1}X_{2}H_{2} + z^{-1}X_{3}H_{1}$$

$$Y_{1} = X_{0}H_{1} + X_{1}H_{0} + z^{-1}X_{2}H_{3} + z^{-1}X_{3}H_{2}$$

$$Y_{2} = X_{0}H_{2} + X_{1}H_{1} + X_{2}H_{0} + z^{-1}X_{3}H_{3}$$

$$Y_{3} = X_{0}H_{3} + X_{1}H_{2} + X_{2}H_{1} + X_{3}H_{0}$$

$$(7)$$

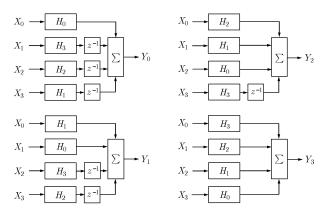

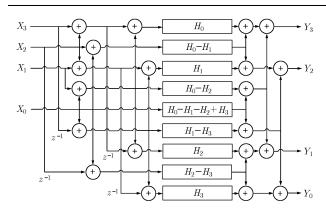

可以得到并行度为 4 的并行 FIR 滤波器的并行结构 实现如图 4 所示。

图 4 并行度为 4 的并行 FIR 滤波器结构

按式(6)对式(4)做 4 相分解,则可分别求得 $Y_0$ ,  $Y_1$ ,  $Y_2$ 和 $Y_3$ :

$$Y_{0} = X_{0}(H_{0} - H_{1} - H_{2} + H_{3}) + (X_{0} + z^{-1}X_{2})$$

$$\cdot (H_{2} - H_{3}) + (X_{0} + z^{-1}X_{3})(H_{1} - H_{3})$$

$$+ (X_{0} + z^{-1}X_{3} + z^{-1}(X_{1} + X_{2}))H_{3}$$

$$Y_{2} = -X_{0}(H_{0} - H_{1} - H_{2} + H_{3}) + (X_{0} + X_{2})$$

$$\cdot (H_{0} - H_{1}) - (X_{0} + z^{-1}X_{3})(H_{1} - H_{3})$$

$$+ (X_{0} + z^{-1}X_{3} + X_{1} + X_{2})H_{1}$$

$$Y_{1} = -X_{0}(H_{0} - H_{1} - H_{2} + H_{3}) - (X_{0} + z^{-1}X_{2})$$

$$\cdot (H_{2} - H_{3}) + (X_{0} + X_{1})(H_{0} - H_{2})$$

$$+ (X_{0} + X_{1} + z^{-1}(X_{2} + X_{3}))H_{2}$$

$$Y_{3} = X_{0}(H_{0} - H_{1} - H_{2} + H_{3}) - (X_{0} + X_{2})$$

$$\cdot (H_{0} - H_{1}) - (X_{0} + X_{1})(H_{0} - H_{2})$$

$$+ (X_{0} + X_{1} + X_{2} + X_{3})H_{0}$$

$$(8)$$

则并行度为 4 的快行 FIR 滤波器结构如图 5 所示。

快行 FIR 滤波器与并行 FIR 滤波器相比,有着极大的资源优势。在并行度为 4,滤波器阶数为 L 的 FIR 滤波器设计为例,其资源利用情况如表 1 所示。

在本设计中,滤波器阶数为L=32,根据表 1,

图 5 并行度为 4 的快行 FIR 滤波器结构

表 1 并行和快行 FIR 滤波器比较

| 项目    | 并行 FIR 滤波器 | 快行 FIR 滤波器           |

|-------|------------|----------------------|

| 乘法器个数 | $4\cdot L$ | 9(L/4)               |

| 加法器个数 | 4(L-1)     | $20+9 \cdot (L/4-1)$ |

并行 FIR 滤波器需要乘法器 128 个,加法器 124 个,而快行 FIR 滤波器只需要乘法器 72 个,加法器 83 个,节省 44%的乘法器以及 33%的加法器。

#### 5 FPGA 中实现

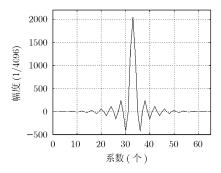

根据微型 SAR 系统参数的要求,采样频率为 2 GHz,通频带截止频率为 450 MHz,阻带截止频率为 550 MHz,本文依据最小均方误差原则设计低通滤波器,阶数为 65 阶,量化位数为 12 b,图 6 为设计出低通滤波器的量化后的系数。图 7 为低通滤波器的频率响应特性,其中实线为系数未量化时的幅频特性,虚线为系数量化后的幅频特性,从图中可以看出,12 位量化对低通滤波器的性能影响很小,其阻带抑制大于 50 dB,带内波动小于 0.02 dB。

该数字下变频模块的重点就是Q路的滤波器的设计,由于设计的低通滤波器的阶数为65阶,Q路滤波器的系数为原低通滤波器的奇数部分,所以系数的个数为32个。对于图4所示的并行FIR滤波器结构和图5所示的快行FIR滤波器结构,利用上面的系数,本文分别编程实现并对两者进行比较。

并行 FIR 滤波器的设计方法是: 首先,将系数进行多相分解,并得到相应的多相系统函数  $\{H_0,H_1,H_2,H_3\}$ ;然后分别实现每一个子滤波器,将每一个子滤波器都重复使用 4 次;最后按照图 4 所示给定输入数据并将输出合成得到最终结果。

快行 FIR 滤波器的设计方法是: 首先,将系数进行多相分解,并得到相应的多相系统函数  $\{H_0,H_1,H_2,H_3\}$ ; 然后,根据  $\{H_0,H_1,H_2,H_3\}$ 分别得到如图 5 所示的 9 个子滤波器系数;接着分别实现得到的 9 个子滤波器;最后按照图 5 所示将各个子滤波器输

入输出合成。

并行 FIR 滤波器和快行 FIR 滤波器都是在 Altera 公司的 StratixII 系列 FPGA 芯片 EP2S90F1020I4 中实现,两者占用资源情况及最高工作时钟速度如表 2 所示。

表 2 滤波器设计结果对比

| 资源项目      | 并行 FIR 滤波器 | 快行 FIR 滤波器 |

|-----------|------------|------------|

| 组合逻辑      | 3172       | 2668       |

| 寄存器       | 4104       | 3647       |

| 工作时钟(MHz) | 322.48     | 341.18     |

从表中可以看出快行 FIR 滤波器比并行 FIR 滤波器所用的资源少 12%左右,但减少并不十分明显,主要原因是滤波器的系数是对称的,在并行 FIR 滤波器中,利用这种对称性导致所需的乘法器数量减少一半,所以减少了 64 个乘法器,还剩下 64 个乘法器;而在快行 FIR 滤波器中,只有一个子滤波器能够利用到这种对称性,所以只能减少 4 个乘法器,还剩下 68 个乘法器。结果导致快行 FIR 滤波器中的乘法器数量反而多于并行 FIR 滤波器,快行 FIR滤波器比并行 FIR 滤波器所用资源减少的主要原因是加法器数量变少导致的。

I 路的延时模块比较简单,共使用 7 个组合逻辑,4 个寄存器和 360 位的存储器,最高工作时钟可以达到 442.09 MHz。

最后采用快行 FIR 滤波器结构实现整个数字下变频模块,共使用 2717 个组合逻辑,3710 个寄存器和382位的存储器,最高工作时钟可以达到310.95 MHz。所用芯片共有 72768 个组合逻辑,72768 个寄存器和 4520448 位的存储器,寄存器的使用量最大也仅占到 5%,还有很多资源供其他运算模块使用。

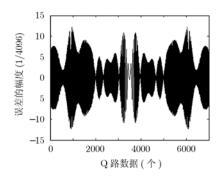

产生一个线性调频信号,在 ModelSim 仿真环境中对设计结果进行仿真,与使用 Matlab 计算的理想结果进行比较,I 路由于只有一个系数而且又是 2的 11 次幂,所以只有移位的操作,不会产生误差,Q 路在结果保留 16 位时的误差如图 8 所示。

#### 6 实际应用结果

整个微型 SAR 系统已经组建完毕,并在 2008 年进行了几次车载试验,由于目标距离较近,所以 发射脉冲的宽度调整为 3 μs,在西安南面秦岭脚下 的环山公路上跑车,天线斜向上对牛头山进行成像, 牛头山地区的成像结果如图 9 所示。

-20

-60

-80

-100

幅度 (dB) -40

图 6 低通滤波器的系数

图 8 FPGA 中实现的量化误差

频率 (MHz)

图 7 低通滤波器的幅频响应

图 9 牛头山成像结果

#### 7 结论

本文依据微型 SAR 的要求,在 FPGA 中实现 了一个高速直接数字下变频模块,该模块采用并行 处理技术提高处理速度,支持采样速度达到 2 Gsps 的应用,实际应用结果显示设计的正确性。该数字 下变频模块也可以应用到其他需要高速直接中频采 样的场合。

### 参考文献

- [1] 苏涛, 何学辉, 吕林夏. 实时信号处理系统设计. 西安: 西安 电子科技大学出版社, 2006: 41-42.

- Su Tao, He Xue-hui, and Lv Lin-xia. Real-time Signal Processing System Design. Xi'an: Xidian University Press, 2006: 41-42.

- 李早社, 禹卫东. 星载SAR实时成像处理器预处理器的FPGA 实现. 现代雷达, 2007, 29(2): 38-40.

- Li Zao-she and Yu Wei-dong. FPGA implementation of preprocessor for spaceborne SAR imaging processor. Modern Radar, 2007, 29(2): 38-40.

- Fudge J, Legako M, and Sehreiner C. An approach to efficient wideband digital down conversion. Proc IC SPAT, Toronto, 1998: 713-717.

- 杨明磊, 陈伯孝, 张守宏. 宽带信号的中频正交采样. 现代雷 达, 2007, 29(3): 47-51.

- Yang Ming-lei, Chen Bo-xiao, and Zhang Shou-hong. Quadrature sampling of wideband IF signal. Modern Radar,

- 2007, 29(3): 47-51.

- 张嵘, 肖先赐. 任意中频带通信号多相数字下变频方法. 电子 与信息学报, 2003, 25(9): 1285-1289.

- Zhang Rong and Xiao Xian-ci. Polyphase based digital down conversion of random IF signal. Journal of Electronics and Information Technology, 2003, 25(9): 1285-1289.

理想 量化

- 李冰, 葛临东, 郑瑾. 一种改进的宽带数字下变频高效结构. [6] 电子与信息学报, 2007, 29(8): 1891-1894.

- Li Bing, Ge Lin-dong, and Zheng Jin. An improved efficient architecture for wideband digital down conversion. Journal of Electronics and Information Technology, 2007, 29(8): 1891-1894.

- Stephan B, Thomas D, and Peter R. A real-time time-domain EMI measurement system for full-compliance measurements according to CISPR 16-1-1. IEEE Transactions on Electromagnetic Compatibility, 2008, 50(2): 259-267.

- Uwe Meyer-Baese. Digital Signal Processing with Field Programmable Aate Arrays (third edition). Springer, 2007: 165 - 207.

- 王虹现: 男, 1979年生, 讲师, 在职博士生, 研究方向为雷达成 像及其实时处理.

- 李 刚: 男,1980年生,硕士,研究方向为雷达成像和实时信号 处理.

- 邢孟道: 男,1975年生,教授,博士生导师,研究方向为雷达成 像和目标识别.

- 张守宏: 男,1938年生,教授,博士生导师,研究方向为雷达信 号处理与检测.