# SHORT COMMUNICATION Properties of Coplanar Type MIS-SIM Structure Chip Capacitor

Y. K. JAIN

Central Electronics Engineering Research Institute, Pilani (Raj.)

and

## S. K. VARSHNEY

S. V. College, ALIGARH, INDIA

(Received June 2, 1980; in final form September 11, 1980)

In MIS-structure, the capacitance depends on applied voltage and its polarity, <sup>1</sup> temperature, <sup>2</sup> oxide thickness and doping level of semiconductor.<sup>3</sup>

Coplanar type MIS-SIM structure has been designed and fabricated on low resistivity silicon. The two electrodes are deposited on the thermal oxide grown on silicon. This structure could be analysed by connecting an MIS structure in series with a SIM structure, thus minimising the voltage and temperature variations on capacitance of the MIS-SIM structure as compared to MIS structure. The coplanar type can be used as a descrete capacitor as well as for hybrid circuits where low VCC & TCC are required.

#### **FABRICATION**

Polished *n*-type silicon wafer of resistivity 0.01 ohm-cm was taken and SiO<sub>2</sub> was grown thermally at 1150°C. Electrodes pattern were deposited by evaporating 99.999% Aluminium at 10<sup>-6</sup> torr vacuum through molybdenum mask. The substrate temperature was kept at 125°C during deposition of elec-

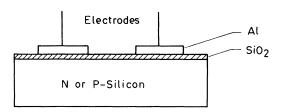

FIGURE 1 Structure of coplanar type MIS-SIM capacitor.

trodes. The wafer was scribed and diced. The chips were die mounted and wire bonded on TO-5 packages. The capacitor structure is as shown in Figure 1.

## MEASUREMENTS AND RESULTS

The capacitance of the encapsulated chip capacitor was measured at 1 KHz. The bias voltage during the capacitance measurement was varied from 0 to  $\pm 100 \text{V}$  and no change in the capacitance value was observed within a measurement accuracy of 0.025%. The capacitor was mounted on a temperature jig so that its temperature could be increased from room temperature to 150 degree centigrade. The change in capacitance was less than 5 ppm/degree centrigrade. Results are summarised in Table I for the varying oxide thickness of the proposed structure.

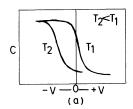

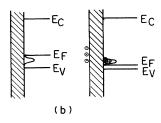

In an MIS structure, the capacitance varies with temperature<sup>2</sup> as shown in Figure 2(a). The variation is due to the change of the Fermi level in the semiconductor as shown in Figure 2(b). At  $T_1$  the Fermi level is assumed to be above the surface states, which are filled with electrons and are neutral. When the temperature is decreased to  $T_2$ , the Fermi level moves closer to the valence band and some of the surface states lose electrons and become positively charged. However, it is assumed that the permittivity of SiO<sub>2</sub> dielectric does not vary with temperature.<sup>4</sup> In the coplanar MIS-SIM structure, the change of Fermi level for the MIS structure due to temperature would be in the opposite direction to the SIM structure, and thus the temperature effect would be minimised.

| TABLE I | T. | A | В | L | Æ | I |

|---------|----|---|---|---|---|---|

|---------|----|---|---|---|---|---|

| Sr. No. | Oxide thickness | Capacitance | No. of capacitors. | TCC     | VCR |

|---------|-----------------|-------------|--------------------|---------|-----|

| 1.      | 0.1150 μm       | 210-220 pf  | 10                 | 5 ppm/C | 0   |

| 2.      | 0.3 500 μm      | 68-73 pf    | 10                 | 3 ppm/C | 0   |

| 3.      | 0.5 000 μm      | 45-48 pf    | 10                 | 3 ppm/C | 0   |

Chip area: 100 mils x 100 mils Electrode Area: 85 mils x 36 mils Separation between Electrodes: 14 mils

FIGURE 2 (a) Capacitance variation of an MIS structure with temperature. (b) Simplified band structure showing change of Fermi level due to temperature (Ref. 2).

The coplanar type MIS-SIM structure chip capacitor is of high quality and is almost independent of changes in voltage and temperature.

### ACKNOWLEDGEMENTS

The authors wish to express their thanks to Dr. B. R. Marathe and Dr. Ashok Srivastava for their encouragement and valuable suggestions.

#### REFERENCES

- 1. A. S. Grove et al, "Investigation of thermally oxidized silicon surfaces using metal-oxide-semiconductor structure", *Solid State Electronics*, 8, 145 (1965).

- 2. P. V. Gray and D. M. Brown, "Density of SiO<sub>2</sub> Si interface states" Appl. Phys. Letters, 8, 31 (1966).

- 3. A. Goetzberger, "Ideal MOS curves for silicon", Bell syst. Tech. J. 45, 1097 (1966).

- A. G. Cockbain, and P. J. Harrop, Brit. J. Appl. Phys. 18, 1109 (1968).