• 工程应用技术与实现 •

文章编号: 1000-3428(2011)24-0236-03

文献标识码: A

中图分类号: TP303

# 多路有序优先级和有序环形仲裁器设计

杨冬勤1,黄 航1,张小燕2,于忠臣1

- (1. 北京工业大学北京市嵌入式系统重点实验室, 北京 100124;

- 2. 北京航空航天大学化学与环境学院,北京 100191)

摘 要:为解决传统仲裁器不能记忆请求顺序的问题,设计多路有序优先级仲裁器和有序环形仲裁器。通过先入先出(FIFO)电路来保存请求的先后顺序,将 FIFO 电路分别与优先级仲裁器和环形仲裁器组合,从而构成有序仲裁器。实验结果表明,该设计能简化复杂度,提高仲裁器处理请求能力,但延时和面积性能略有下降。

**关键词:** 有序仲裁器; 优先级仲裁器; 环形仲裁器; 先入先出电路; 令牌

# Design of N-way Ordered Priority and Ordered Ring Arbiter

YANG Dong-qin<sup>1</sup>, HUANG Hang<sup>1</sup>, ZHANG Xiao-yan<sup>2</sup>, YU Zhong-chen<sup>1</sup>

- (1. Embedded System Key Lab of Beijing, Beijing University of Technology, Beijing 100124, China;

- 2. School of Chemistry and Environment, Beihang University, Beijing 100191, China)

[Abstract] To improve shortcoming of traditional arbiters, this paper proposes N-way ordered arbiter, which is based on combination of First In First Out(FIFO) and priority arbiter and ring arbiter respectively. FIFO is used for savingthe request orders. It proposes a new structure of priority and a new ring arbiter. Results show that, modular design simplifies the complexity, improves the ability of arbiter to process the request, and the ability of saving the request in order reduces latency and area properties.

**[Key words]** ordered arbiter; priority arbiter; ring arbiter; First In First Out(FIFO) circuit; token

DOI: 10.3969/j.issn.1000-3428.2011.24.079

#### 1 概述

仲裁器在高性能的路由器、处理器、通信系统使用广泛。 当有多个请求时,一般的仲裁器如 round-robin 仲裁器<sup>[1]</sup>、优 先级仲裁器<sup>[2]</sup>、网格仲裁器<sup>[3]</sup>等,授权不能按请求的先后顺 序进行,但有序仲裁器可以,本文在 Bystrov 提出有序仲裁 器<sup>[4]</sup>的基础上解决了亚稳态问题和请求路数限制。

### 2 有序仲裁器的设计

#### 2.1 FIFO 电路

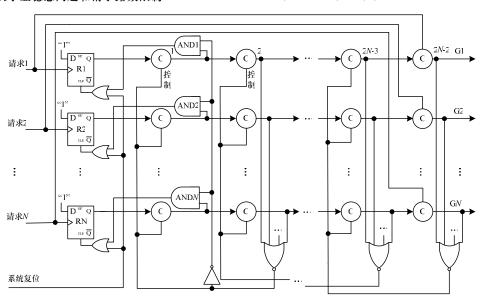

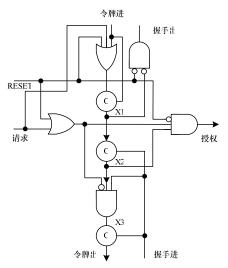

先入先出(First In First Out, FIFO)电路结构 $^{(4)}$ 能够保存请求顺序,如图 1 所示,它依次由  $Gi(i=1,2,\cdots,N)$ 输出,FIFO输出信号严格按照先入先出的顺序。C-门 $^{(4)}$ 的特征方程为:

$Qn+1=AB+(A\oplus B)Qn$

图 1 多路 FIFO 电路

FIFO 电路的工作原理如下:

- (1)RESET=1,初始化电路。然后RESET=0。

- (2)请求 1 产生上升脉冲, 寄存器 R1 的 Q 端输出 1。

**作者简介**: 杨冬勤(1986-), 男, 硕士研究生, 主研方向: 数字电路设计; 黄 航、张小燕, 硕士研究生; 于忠臣, 教授、博士生导师

**收稿日期:** 2011-06-28 **E-mail:** dongqiny@126.com

(3)因为 R1 后所有 C-门的控制信号为 1, 所以 R1 输出的 1 传递到最后一个 C-门的输出,则 G1 为 1。

(4)第一行 C-门的输出全为 1,则所有的或非门输出为 0,即所有 C-门的控制变为 0。

(5)AND1 的输出为 1,则寄存器 R1 的 clear 端为 1, R1 被清零。

(6)最后一列,第一行 C-门的输出保持为 1, 其他 C-门的输出变为 0。

(7)如果有其他的请求,将锁定在倒数第 3 列 C-门。往后的请求依此类推。

#### 2.2 有序优先级仲裁器

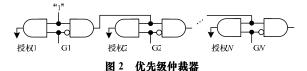

如果有 2 路或更多请求脉冲同时产生,因为 FIFO 电路不会作区分的保存,所以 FIFO 电路的输出  $Gi(i=1,2,\cdots,N)$ 也会有 2 路或 2 路以上同时为 1 的情况。如果这时把 FIFO 电路输出给如图 2 所示线性优先级仲裁器,其输出按照请求的先后顺序授权,从而实现了有序优先级仲裁器。

#### 2.3 有序环形仲裁器

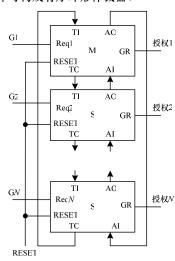

如图 3 所示的环形仲裁器是无优先级的仲裁器, FIFO 电路和它组合即可构成有序环形仲裁器。

图 3 环形仲裁器

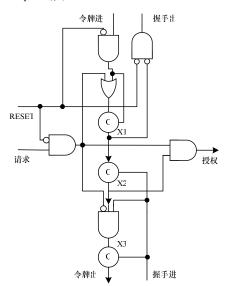

N 路环形仲裁器由一个主节点和 N-1 个从节点构成。节点中,X2=1 表示获得令牌,X2=0 表示没有。同一时刻环路内有且只有一个节点有令牌<sup>[5]</sup>。在 RESET=1 时,从节点(见图 4)失去令牌,主节点(见图 5)获得令牌。

对于从节点, RESET=1, 使 X1=X2=X3=0, TO=AO=GR=0; RESET=0 时进入工作状态, 假设有请求 REQ=1, 并有令牌传入 TI=1, 其工作过程如下:

- (1)令牌输入 TI=1, REQ=1,则 X1=1,准备获取令牌。

- (2)因为此时本节点无握手输入,即 AI=1,所以 X2=1,获得令牌。

- (3)令牌握手输出 AO=0, 使上一节点令牌脉冲结束,即TI=0,又因为 REQ=1,所以 X1=1 一直保持。

- (4)授权 GR=1, X3=0。

- (5)一段时间后请求撤销 REQ=0,则授权解除 GR=0,X1=0。

(6)REQ=0,则 X3=1,令牌输出 TO=1,准备交出令牌。

(7)下一节点收到令牌脉冲后,产生令牌握手低脉冲AI=0,X2=0,X3=0,本节点的令牌脉冲结束TO=0,令牌已交出;如果节点没有请求REQ=0,当它收到令牌输入时,工作步骤同上,但不包括步骤(4)和步骤(5)。

其中, TI: 令牌进; TO: 令牌出; AO: 握手进; AI: 握手出; ReqN: 请求 N。

图 4 从节点

图 5 主节点

主节点在工作状态(RESET=0)和从节点的功能完全相同。只是 RESET=1 时,主节点获得令牌,X1=X2=1,X3=0,GR=AI=AO=0;RESET=0 时,若主节点有请求 REQ=1,则授权输出 GR=1,X3=0 使得令牌锁定在主节点,等到请求撤销 REQ=0 时,X1=0,X3=1,此时握手输入为 AI=1,所以令牌输出 TO=1,下一节点收到令牌输出后产生握手输入低脉冲,使 AI=0,则 X2=X3=TO=0;清除了该节点的令牌和令牌输出脉冲。

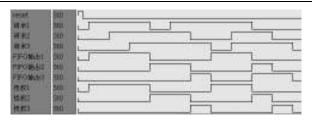

在如图 3 所示的环形仲裁器中,所有请求  $Gi(i=1,2,\cdots,N)$  或非后连到 RESET。  $Gi=0(i=1,2,\cdots,N)$ 时,RESET=1;只要任一节点有请求,则所有节点的 RESET=0,令牌将在环内流动,找到有请求的节点停下来,直到请求撤销。当有 2 个或 2 个以上节点同时存在请求时,将按照令牌获得顺序依次被授权,这种授权是不存在优先级的,如图 6 所示。

图 6 N=3 有序环形仲裁器仿真波形界面图

# 3 性能分析

#### 3.1 延时

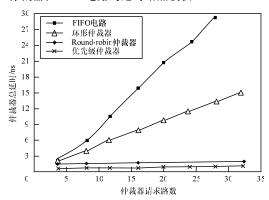

本文采用中芯国际(SMIC)130 nm 逻辑工艺库,对仲裁器和 FIFO 电路做综合后并分析延时,结果如图 7 所示。可见在本设计中,随着仲裁路数增加:优先级仲裁器的延时变化最小,优于 Round-robin 仲裁器; FIFO 电路的延时增加较快。

图 7 仲裁器延时与请求路数关系

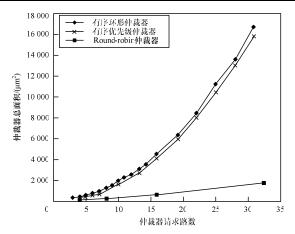

#### 3.2 面积

本文采用中芯国际(SMIC)65 nm 高密度(high density)逻辑工艺库,使用 DC(Design Compiler)对仲裁器做综合并分析面积,结果如图 8 所示。可知,令仲裁器的请求路数为 N,则有序优先级仲裁器和有序环形仲裁器的面积近似和  $N^2$  成正比,而 Round-robin 仲裁器的面积随 N 近似线性递增。所以,随着 N 的增加,有序仲裁器比 Round-robin 仲裁器面积的增加快很多。

图 8 仲裁器面积与请求路数关系

#### 4 结束语

本文分别实现了一种具有记忆功能的有序优先级仲裁器和有序环形仲裁器,该设计可用 EDA 工具综合实现,对于数字电路中的仲裁问题有一定的应用价值。本文的仲裁器还有不足之处,如随着请求路数增大,2 种仲裁器的延时线性递增,面积曲线增长,在今后的研究中需要不断地改进和完善。

## 参考文献

- [1] Shin E S, Mooney V J, Riley G F. Round-robin Arbiter Design and Generation[R]. Atlanta, USA: Georgia Institute of Technology, Tech. Rep.: GIT-CC-02-38, 2002.

- [2] Plummer W W. Asynchronous Arbiters[J]. IEEE Transactions on Computers, 1972, 21(1): 37-42.

- [3] 张俊钦, 谷大武, 侯方勇. 改进的仲裁器 PUF 设计与分析[J]. 计算机工程, 2010, 36(3): 249-250.

- [4] Bystrov A, Yakovlev A. Ordered Arbiters[J]. Electronics Letters, 1999, 35(11): 877-879.

- [5] Low K S, Yakovlev A. Token Ring Arbiters: An Exercise in Asynchronous Logic Design with Petri Nets[R]. Newcastle, UK: University of Newcastle Upon Tyne, Tech. Rep.: No. 537, 1995.

编辑 任吉慧

#### (上接第 235 页)

# 6 结束语

本文研究了基于动态故障树的网络化故障诊断技术在飞机 CSCF-AC 电源系统故障诊断中的应用,并设计开发了一个飞机电源网络化故障诊断系统,将飞机、地面维修部门和远程专家联系起来,在不同层次上对飞机电源系统故障进行诊断。实验结果表明,该系统具有一定的实用性,为飞机电源系统故障的分析和诊断提供了一种新的思路。

#### 参考文献

- [1] 朱新宇. 飞机电源智能监控系统[M]. 成都: 西南交通大学出版社, 2002.

- [2] Dugan J B, Bavuso S J, Boyd M A. Dynamic Fault-tree Models for

- Fault-tolerant Computer Systems[J]. IEEE Transactions on Reliability, 1992, 41(3): 363-377.

- [3] 陈越洲, 谭 琳, 邢维艳, 等. 一种新的故障树定性分析方法[J]. 计算机工程, 2008, 34(13): 67-69.

- [4] Merle G, Roussel J M. Algebraic Modeling of Fault Trees with Priority and Gates[C]//Proc. of the 1st IFAC Workshop on Dependable Control of Discrete Systems. Cachan, France: [s. n.], 2007: 175-180.

- [5] Merle G, Roussel J M, Lesage J J, et al. Probabilistic Algebraic Analysis of Fault Trees with Priority Dynamic Gates and Repeated Events[J]. IEEE Transactions on Reliability, 2010, 59(1): 250-260.

编辑 任吉慧