# 10Gb/s Silicon Modulator Based on Bulk-Silicon Platform for DRAM Optical Interface

## K. -H. Lee, D.J. Shin, H. -C. Ji, K. W. Na, S. G. Kim, J. K. Bok, Y. S. You, S. S. Kim, I. S. Joe, S. D. Suh, J. H. Pyo, Y. H. Shin, K. H. Ha, Y. D. Park, and C. H. Chung

Image architecture Lab., semiconductor R&D center, Samsung electronics, San #24 Nongseo-dong, Giheung-gu, Yongin-si,Gyeonggi-do, 446-711 Korea E-mail : <u>khyun7.lee@samsung.com</u>

**Abstract:** We present 10Gb/s silicon Mach-Zehnder modulators fabricated on a bulk silicon wafer. 10Gb/s data transmission with extinction ratio of >9dB at de-emphasis level of 12dB is successfully demonstrated.

OCIS codes: (130.0250) Optoelectronics; (230.4110) Modulators

### 1. Introduction

Recently, it has been a critical issue to increase the memory I/O data bandwidth in high performance computing systems. The memory bandwidth can be increased by expanding the data bus width or raising the per-pin data rate [1, 2]. In general, many efforts have focused on increasing the per-pin data rate since the wider bus width requires larger board area and higher power, resulting in the higher system cost [2]. However, the practical limitation exists in increasing the per-pin data rate due to large conductive and dielectric losses of copper-based electrical lines.

The optical interconnect is capable of providing the required per-pin data rate since optical channels have low propagation loss with negligible frequency dependence. In particular, a bulk-silicon based optical interconnect technology is more attractive to cost-sensitive applications such as a dynamic random access memory (DRAM) interface than a typical approach using a silicon-on-insulator (SOI) platform. A few studies have been tried to fabricate passive and active components with a bulk-silicon approach [3-6] and we have already demonstrated 5Gb/s data modulation with a Mach-Zehnder modulator (MZM) fabricated on a bulk-silicon wafer [5]. In this paper, we report successful demonstration of 10Gb/s data transmission based on a bulk-silicon MZM modulator by applying the de-emphasis technique.

### 2. Experimental setup

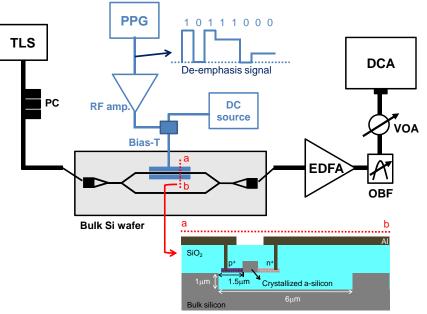

Fig. 1. Cross-sectional diagram of the active part of the modulator and experimental setup for 10Gb/s data transmission. (TLS: Tunable laser source, PC: Polarization controller, PPG: Pulse pattern generator, EDFA: Erbium-doped fiber amplifier, OBF: Optical band-pass filter, VOA: Variable optical attenuator, DCA: Digital communication analyzer)

## JThA33.pdf

Fig. 1 shows the cross-sectional diagram of the active part of the modulator as well as the experimental set-up used for 10Gb/s data transmission. The bulk-silicon modulator used in this experiment has the same structure with that of a typical carrier-injection-type PIN MZM modulator except local oxide undercladding. In order to form the undercladding, the trench  $(6\times1 \ \mu\text{m}^2)$  was etched in a bulk-silicon substrate, filled with oxide, and planarized by the chemical mechanical polishing process. The waveguide core having the size of  $\sim500\times\sim250 \ \text{nm}^2$  was crystallized by the solid phase epitaxy (SPE) technique from amorphous silicon. The detailed fabrication process and condition can be shown in [5, 6]. The modulator active length is 200 $\mu$ m and the distance between the p+ and n+ regions and the edge of the waveguide core is 0 nm for the high speed modulation, although it induces relatively high optical on-chip loss of ~13dB.

As shown in the figure, the optical carrier at the wavelength of 1550nm generated by a tunable laser source is vertically coupled to the bulk-silicon modulator through the grating coupler fabricated on the same wafer and the injected optical signal is modulated by a de-emphasized non-return-to-zero (NRZ) pseudo-random binary sequence (PRBS) signal from a pulse pattern generator (PPG). Finally, the modulated optical signal is emitted from the modulator via an output grating coupler and analyzed by a digital communication analyzer (DCA) after passing through an erbium-doped fiber amplifier (EDFA) for compensation of the coupling and on-chip loss, an optical band-pass filter (OBPF) for filtering out amplitude spontaneous noise, and a variable optical attenuator (VOA) for avoiding DCA saturation .

The de-emphasis method, where the following bits in a series of ones or a series of zeros are attenuated, is commonly used in serial interfaces to reduce the effects of Inter Symbol Interference. With the de-emphasis, the spectral energy of the PRBS signal is reduced at low frequencies and it counteracts the high frequency loss characteristic of the modulator, resulting in a flat modulation response which makes it possible to transmit high speed data. In this experiment, the attenuation level, called a de-emphasis level, was adjusted to optimize the eye quality.

#### 3. Experimental results

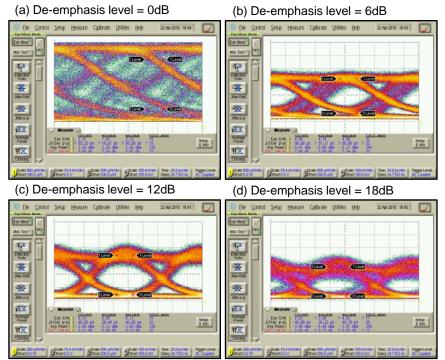

Fig. 2. Measured 10Gb/s optical eye diagrams for (a) without de-emphasis, (b) de-emphasis level = 6dB, (c) de-emphasis level = 12dB, and (d) de-emphasis level=18dB. (AC:  $2^{31}$ -1 PRBS NRZ data having 4.2Vpp, DC: 0.3V)

Fig.2 shows the measured optical eye diagrams at different de-emphasis levels. The results were obtained by applying de-emphasized 10Gb/s  $2^{31}$ -1 PRBS NRZ bit streams having the peak-to-peak amplitude of 4.2V to the modulator with DC bias of 0.3V. As shown in the figure, the eye-opening depends on the de-emphasis level and the extinction ratio (ER) of >9dB can be obtained at 10Gb/s with the de-emphasis level of 12dB. Although the eye

## JThA33.pdf

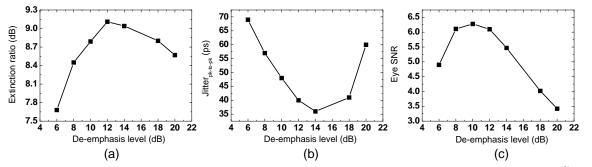

height is decreased with the de-emphasis level, the ER can be increased since the de-emphasis technique can reduce the fluctuation of low and high levels. This can be more clearly shown in Fig. 3 showing the measured ER, jitter<sub>pk-to-pk</sub>, and eye signal-to-noise ratio (SNR). Below the de-emphasis level of around 12dB, the eye quality is improved with the de-emphasis level because ER is increased and the jitter<sub>pk-to-pk</sub> is decreased, respectively. The jitter<sub>pk-to-pk</sub> reduction is mainly due to decrease of the pattern-dependent jitter by signal de-emphasis. From the results, it can be confirmed that the modulator used in this experiment has good eye performance at 10Gb/s with the emphasis level of 10~12 dB.

Fig. 3. Plot of (a) ER, (b) Jitter<sub>pk-to-pk</sub>, (c) Eye SNR as a function of de-emphasis level at the fixed AC and DC conditions.(AC: 10Gb/s 2<sup>31</sup>-1 PRBS NRZ data having 4.2Vpp, DC: 0.3V)

## 3. Conclusion

We demonstrated the 10Gb/s PRBS data transmission with the bulk-silicon PIN MZM having local oxide undercladding and the crystallized silicon layer by a solid phase epitaxy method. For the successful demonstration, the de-emphasis technique was applied and the extinction ratio of >9dB at 10Gb/s was obtained with the de-emphasis level of 12dB. We believe that this bulk-silicon approach can be useful for cost-sensitive applications such as a DRAM interface.

#### References

1. H. Lee, et al, "A 16 Gb/s/Link, 64 Gb/s Bidirectional Asymmetric Memory Interface," JSSC 44, 1235-1247 (2009).

2. K. -H. Kim, et al, "A 20-Gb/s 256-Mb DRAM With an Inductorless Quadrature PLL and a Cascaded Pre-emphasis Transmitter," JSSC 41, 127-134 (2006).

3. N. Wherwood-Droz, *et al*, "Oxidized Silicon-On-Insulator (OxSoi) from bulk silicon: a new photonic platform," Opt. Express **18**, 5785-5790 (2010).

4. K. Preston, et al, "Deposited silicon high-speed integrated electro-optic modulator," Opt. Express 17, 5118-5124 (2009).

5. D.-J. Shin, et al, "Mach-Zehnder Silicon Modulator on Bulk Silicon Substrate; Toward DRAM Optical Interfaces," GFP2010, ThC7 (2010).

6. H. -C. Ji, et al, "Bulk-Silicon Photonic Wire for One-Chip Integrated Optical Interconnection," GFP2010, P1.11 (2010).