# Analysis of 1/f noise in CMOS APS

## Hui Tian, and Abbas El Gamal

# Information Systems Laboratory, Stanford University Stanford, CA 94305 USA

## ABSTRACT

As CMOS technology scales, the effect of 1/f noise on low frequency analog circuits such as CMOS image sensors becomes more pronounced, and therefore must be more accurately estimated. Analysis of 1/f noise is typically performed in the frequency domain even though the process is nonstationary. To find out if the frequency domain analysis produces acceptable results, the paper introduces a time domain method based on a nonstationary extension of a recently developed, and generally agreed upon physical model for 1/f noise in MOS transistors. The time domain method is used to analyze the effect of 1/f noise due to pixel level transistors in a CMOS APS. The results show that the frequency domain results can be quite inaccurate especially in estimating the 1/f noise effect of the reset transistor. It is also shown that CDS does not in general reduce the effect of the 1/f noise.

Keywords: 1/f noise, subthreshold operation, nonstationary 1/f noise model, time domain noise analysis, CMOS APS, image sensor

## 1. INTRODUCTION

As CMOS technology scales, the effect of 1/f noise on low frequency analog circuits such as CMOS image sensors becomes more pronounced.<sup>1</sup> As a result it is becoming important to estimate the effect of 1/f noise more accurately. Analysis of 1/f noise is typically performed in the frequency domain. The 1/f noise, which is nonstationary, is approximated by a stationary band-limited process. A low cutoff frequency  $f_L$ is defined based on the circuit on-time  $t_{on}$  and a high cutoff frequency  $f_H$  is defined based on the circuit frequency response. The average output noise power is then calculated by finding the area under the output power spectral density curve. The low cutoff frequency is typically, and somewhat arbitrarily, set equal to  $\frac{1}{t_{on}}$ . In order to find out if the frequency domain method produces accurate results one needs an accurate nonstationary model for the 1/f noise and use time domain analysis.

The origin of 1/f noise in MOS transistors has been the subject of great study and controversy.<sup>2,3</sup> Recent studies of small area sub-micron MOS transistors<sup>4,5</sup> have, to a large extent, resolved the controversy and there is now a generally agreed upon physical model for 1/f noise.<sup>6–8</sup> This model, however, implicitly assumes an infinite circuit on-time and thus stationarity, which is not compatible with the operation of real circuits. In this paper we extend this 1/f noise model to handle finite circuit on-time. This makes it possible to estimate the effect of the 1/f noise more accurately using time domain analysis.<sup>9</sup> As an example, we use our model to analyze the effect of 1/f noise due to pixel level transistors in a CMOS APS.

The rest of the paper is organized as follows. In section 2 we describe the agreed upon noise model for a single active trap in the gate oxide of an MOS transistor and the resulting stationary 1/f noise model. We then describe our nonstationary extension of the model. In section 3 we review the pixel circuit and operation of a CMOS photodiode APS and analyze the 1/f noise due to the follower and access transistors using time domain analysis and our nonstationary 1/f noise model. We find that the results are approximately twice as large as the results obtained using frequency domain analysis. In section 4 we analyze the 1/f noise due to the reset transistor. Here we use the subthreshold time-varying circuit model in addition to our nonstationary noise model. We find that the frequency domain results are very inaccurate: over a factor of 11 lower than time domain analysis in some cases. We briefly discuss the effect of CDS on 1/f noise in the last section.

Other author information: Email: huitian@isl.stanford.edu, abbas@isl.stanford.edu; Telephone: 650-725-9696; Fax: 650-723-8473

## 2. PHYSICS BASED 1/F NOISE MODEL

1/f noise (sometimes also called flicker noise, or low frequency noise), in the strictest sense, refers to the noise whose power spectral density (psd) is inversely proportional to frequency, *i.e.*,  $S_N \propto \frac{1}{|f|}$ . More generally, noise with  $S_N \propto \frac{1}{|f|^{\beta}}$ , for  $\beta > 0$ , is also called 1/f noise (or 1/f like noise). In addition to electronic devices, 1/f noise also appears in many other devices and natural phenomena, such as oscillation of quartz crystals, geophysical records, economic data, traffic-flow rates, image texture, heart beat rates, ..., just to name a few. As a result, the origin of 1/f noise has been the subject of numerous studies in many different fields. Unfortunately, since 1/f psd is not integrable, it is not a valid psd of stationary processes and there is no agreed upon universal mathematical or physical model to describe it. In the next subsection we describe the most widely accepted physical model for MOS transistors 1/f noise. In the following subsection we describe our nonstationary extension of this model which will be used to analyze the effect of 1/f noise in the APS circuit.

## 2.1. Stationary 1/f noise model

In this paper we are mainly concerned with 1/f noise in MOS transistors. Over the last three decades, two main theories of 1/f noise in MOS transistors were developed, namely the carrier number fluctuation theory, and the mobility fluctuation theory.<sup>3</sup> The carrier number fluctuation theory attributes 1/f noise to random capture and emission of conduction channel carriers by traps in the gate oxide, while the mobility fluctuation theory considers the 1/f noise as a result of the fluctuation in the carrier mobility. Both theories succeeded in partially explaining some of the experimental data. However, since it was very difficult to experimentally verify the noise generation mechanism, there was no conclusive evidence to support either theory.

This controversy has, to a large extent, been resolved by recent studies of small area sub-micron MOS transistors. In these transistors, very few, (sometimes only one) traps are active in the gate oxide. Capture and emission of a single channel carrier result in discrete modulation of the channel current, which can be modeled as a random telegraph signal (RTS). Note that no more than one electron can occupy a trap at any point in time and thus the trapped electron number N(t) switches between two states, 1 and 0. It is well known that the autocovariance of N(t) is  $C_{\lambda}(\tau) = \frac{1}{4}e^{-2\tau\lambda}$ , and the psd is  $S_{\lambda}(f) = \frac{1}{4}\frac{\lambda}{\lambda^2 + (\pi f)^2}$ , where  $\lambda$  is the transition rate.

Superposition of multiple independent RTSs with some distribution on  $\lambda$ , gives rise to the unified number and mobility theory of 1/f noise.<sup>8</sup> In this widely accepted theory, the distribution of  $\lambda$  obeys a log uniform law

$$g(\lambda) = \frac{4kTAt_{ox}N_t}{\lambda\log\frac{\lambda_H}{\lambda_r}},\tag{1}$$

where kT is the thermal energy, A is the channel area,  $t_{ox}$  is the effective gate oxide thickness,  $N_t$  is the gate oxide trap density ( $ev^{-1}cm^{-3}$ ),  $\lambda_H$  is the fastest transition rate, and  $\lambda_L$  is the slowest transition rate. The sum of the trapped electron numbers, thus, has the psd

$$S(f) = \int_{\lambda_L}^{\lambda_H} S_{\lambda}(f) g(\lambda) d\lambda \approx \frac{kT A t_{ox} N_t}{2f \log \frac{\lambda_H}{\lambda_L}} = \frac{kT A N_t}{2\gamma f},$$

(2)

where  $t_{ox}$  is the gate oxide thickness, and  $\gamma$  is a constant \*.

From this trapped electron number psd, we can find the drain current 1/f noise psd by performing the MOS transistor charge-control analysis. As reported recently,<sup>7,11</sup> for sub-micron nMOS transistors no mobility fluctuations are observed, and thus the drain current 1/f noise psd is given by

$$S_{I_d}(f) = g_m^2 S_{V_g}(f) = g_m^2 \frac{1}{C_{ox}^2} S_{Q_{ch}}(f) = g_m^2 \frac{1}{C_{ox}^2} (\frac{q}{A})^2 S(f) = \frac{g_m^2 q^2 k T N_t}{2C_{ox}^2 A \gamma f},$$

(3)

<sup>\*</sup>There are several models available in explaining the wide distribution of traps both in space and in energy, inside the gate oxide. The exact meaning of  $\gamma$  depends on the specific model. Simple models often treat it as the tunneling constant.<sup>10</sup>

where  $C_{ox}$  is the gate oxide capacitance,  $g_m$  is the transconductance,  $S_{V_g}(f)$  is the equivalent gate voltage 1/f noise psd, and  $S_{Q_{ch}}(f)$  is the channel charge density 1/f noise psd. Note that  $S_{I_d}(f)$  is inversely proportional to the gate area, which explains the reason why 1/f noise is becoming more pronounced as technology scales.

Circuit designers typically use the SPICE 1/f noise model where  $S_{V_g}(f) = \frac{k_F}{2C_{ox}Af}$  and are given the value of the parameter  $k_F$ . From equation 3, we find that  $k_F = \frac{q^2 k T N_t}{C_{ox}\gamma}$ . This shows the correspondence of the physics based 1/f noise model to the SPICE model.

A more general unified number and mobility theory is needed to find the drain current 1/f noise psd for a pMOS transistor. Since we are only concerned with nMOS transistors here, we do not describe this theory. The following analysis, however, can be directly applied to pMOS transistors.

#### 2.2. Nonstationary extension

The analysis of 1/f noise in circuits is typically performed by first approximating the noise by a stationary band-limited process and using frequency response analysis. This requires choosing both a high and a low cutoff frequency. The high cutoff frequency  $f_H$  is determined by the frequency response of the circuit which is well defined. The low cutoff frequency  $f_L$  on the other hand is somewhat arbitrarily set to  $\frac{1}{t_{on}}$ , where  $t_{on}$  is the circuit on-time. In this subsection, we briefly discuss our nonstationary extension to the 1/f noise theory presented in the previous subsection, which avoids the use of  $f_L$ . More detailed description can be found elsewhere.<sup>12</sup>

In deriving this extended model, we found the autocovariance function of N(t) to be

$$\mathcal{C}_{\lambda}(t,\tau) = \frac{1}{4}e^{-2\lambda\tau}(1-e^{-4\lambda t}).$$

(4)

If we let  $t \to \infty$ ,  $C_{\lambda}(t,\tau)$  converges to  $C_{\lambda}(\tau) = \frac{1}{4}e^{-2\lambda\tau}$ , which is the stationary autocovariance discussed in the previous subsection.

The autocovariance of the total trapped electron number of a large area MOS transistor, with many independent active traps in its gate oxide, is simply the summation of the RTS autocovariance of each trap. Note that here we perform the summation directly in time domain

$$\mathcal{C}(t,\tau) = \int_{\lambda_L}^{\lambda_H} \mathcal{C}_{\lambda}(t,\tau) g(\lambda) d\lambda.$$

(5)

Applying charge-control analysis as we did in deriving equation 3, we get the resulted mean square gate voltage as

$$\overline{V_g^2(t)} = \left(\frac{q}{AC_{ox}}\right)^2 \int_{\lambda_L}^{\lambda_H} \mathcal{C}_\lambda(t,0)g(\lambda)d\lambda.$$

(6)

This integral does not have a closed form solution, and must be evaluated numerically.

We now compare the 1/f noise power computed using the conventional frequency domain method to the more accurate time domain method described. For the comparison and for the remainder of the paper we assume that  $t_{ox} = 7$ nm,  $\gamma = 10^8$  cm<sup>-1</sup>,  $\lambda_H = 10^{10}$  s<sup>-1</sup>, and  $N_t = 10^{17}$  eV<sup>-1</sup> cm<sup>-3</sup>. These are typical values for a 0.35 $\mu$  CMOS process. From these numbers we get that  $\lambda_L = 4 \times 10^{-21}$ ,  $C_{ox} = 5$  fF $\mu$ m<sup>-2</sup>, and  $k_F = 5 \times 10^{-24}$ V<sup>2</sup>F at T = 300K.

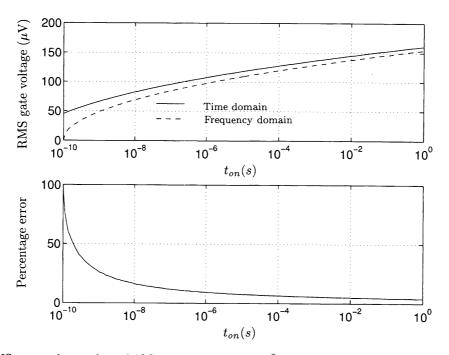

In Figure 1, we plot the RMS gate voltage  $\sqrt{V_g^2}$  due to the 1/f noise as a function of the circuit on-time  $t_{on}$  using both the frequency domain and the time domain methods. Shown in the bottom half of the figure is the error using the frequency domain analysis as a percentage of to the more accurate time domain analysis curve. As expected the error percentage decreases as  $t_{on}$  increases. In this example, we assume that the channel area  $A = 1\mu m^2$ .

Figure 1. RMS gate voltage of an nMOS transistor with  $1\mu m^2$  channel area (top) and the percentage error using the frequency domain method (bottom).

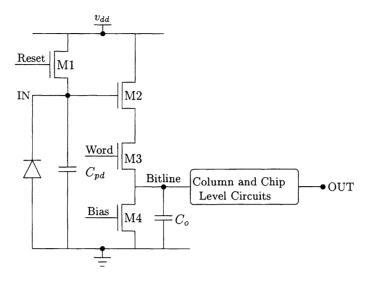

## 3. 1/F NOISE SOURCES IN APS PIXEL

The photodiode APS circuit we analyze in this paper is the standard three transistors per pixel circuit shown in Figure 2. Each pixel comprises in addition to a photodiode, a reset transistor M1, a source follower transistor M2, and an access transistor M3. The capacitor  $C_{pd}$  shown in the figure represents the equivalent photodiode capacitance. To complete the signal path we also show the column bias transistor and storage capacitor  $C_o$ . We only analyze the 1/f noise generated within the pixel. The 1/f noise effect due to column and chip level circuits can be treated using the same method presented in this paper. We assume that all pixel level transistors have the same length  $L = 0.7\mu m$  and width  $W = 1.4\mu m$ ,  $C_o = 3pF$ , and that  $C_{pd} = 22fF$  during reset. These parameters are chosen to demonstrate results and are not necessarily optimized for low noise operation.

We are interested in finding the output referred 1/f noise RMS value at Bitline in volts. To compute this value, we consider the 1/f noise generated during each phase of the APS operation, *i.e.*, during reset, integration, and readout.

During integration, the 1/f noise is primarily generated by the photodiode. It is due to surface recombination of carriers, and the fluctuation in bulk carrier mobility.<sup>13</sup> For a reverse or none biased photodiode, the 1/f noise is not directly related to the total current. Instead, it is a function of the dark current, and is typically much smaller than the dark current shot noise, and can thus be ignored.

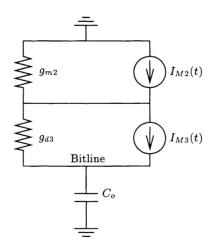

During readout, the 1/f noise is due to the source follower transistor M2, and the access transistor M3. Depicted in Figure 3 is the small signal model of the APS pixel circuit during readout, where  $I_{M2}(t)$  and  $I_{M3}(t)$  are the 1/f noise current sources associated with M2 and M3, respectively,  $g_{m2}$  is the transconductance of M2,  $g_{d3}$  is the channel conductance of M3, and  $C_o$  is the column storage capacitance.

Let  $C_{M2} = (1 + \frac{g_{m2}}{g_{d3}})C_o$  and  $C_{M3} = (1 + \frac{g_{d3}}{g_{m2}})C_o$ , we get the Bitline voltage due to the noise current sources

$$V_{M2}(t) = \frac{e^{-\frac{g_{m2}}{C_{M2}}t}}{C_{M2}} \int_0^t I_{M2}(s) e^{\frac{g_{m2}}{C_{M2}}s} ds,$$

(7)

171

Figure 2. APS circuit.

Figure 3. Small signal model for 1/f noise analysis during readout.

and

$$V_{M3}(t) = \frac{e^{-\frac{g_{d3}}{C_{M3}}t}}{C_{M3}} \int_0^t I_{M3}(s) e^{\frac{g_{d3}}{C_{M3}}s} ds.$$

(8)

Therefore, the mean square 1/f noise voltage due to each source is given by

$$\overline{V_{M2}^2(t)} = \left(\frac{qg_{m2}}{AC_{ox}}\right)^2 \frac{e^{-\frac{2g_{m2}}{C_{M2}}t}}{C_{M2}^2} \int_0^t \int_0^t \int_{\lambda_L}^{\lambda_H} g(\lambda) \mathcal{C}_\lambda(s_1, |s_2 - s_1|) e^{\frac{g_{m2}}{C_{M2}}(s_1 + s_2)} d\lambda ds_1 ds_2, \tag{9}$$

$\operatorname{and}$

$$\overline{V_{M3}^2(t)} = \left(\frac{qg_{m3}}{AC_{ox}}\right)^2 \frac{e^{-\frac{2g_{d3}}{C_{M3}}t}}{C_{M3}^2} \int_0^t \int_0^t \int_{\lambda_L}^{\lambda_H} g(\lambda) \mathcal{C}_\lambda(s_1, |s_2 - s_1|) e^{\frac{g_{d3}}{C_{M3}}(s_1 + s_2)} d\lambda ds_1 ds_2.$$

(10)

As a numerical example, we assume that the nMOS transistor mobility is  $\mu = 550 \text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ , the bias current is  $i_d = 1.8\mu\text{A}$ , the reverse bias voltage on the photodiode is  $v_{pd} = 1.8\text{V}$ , and the threshold voltage is  $v_{th} = 0.9\text{V}$  (with body effect). The transconductance of M2 thus is  $g_{m2} \approx \sqrt{2i_d\mu C_{ox}W/L} = 4.4 \times 10^{-5}\Omega^{-1}$ .

Since M3 is operating in the linear region and the voltage difference between its drain and source is very small, we can write

$$g_{d3} \approx \mu C_{ox} W / L (v_{G3} - v_{D3} - v_{th}), \tag{11}$$

where  $v_{G3} = 3.3$ V is the gate voltage of M3. Note that  $v_{D3} = v_{pd} - \sqrt{\frac{2i_d}{\mu C_{ox} W/L}} - v_{th}$ . Substituting into equation 11, we get that  $g_{d3} = 8.7 \times 10^{-4} \Omega^{-1}$ . Consequently the transconductance of M3  $g_{m3} \approx \frac{i_d}{v_{G3} - v_{S3} - v_{th}} = 1.1 \times 10^{-6} \Omega^{-1}$ .

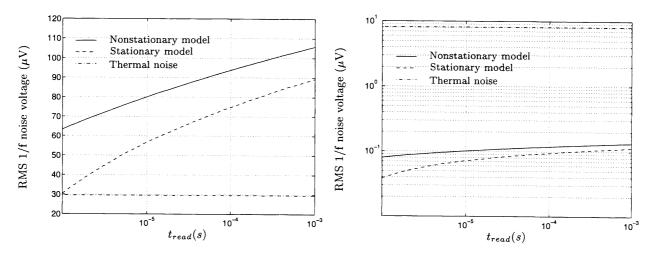

Now we can numerically evaluate equations 9 and 10 to find the Bitline RMS noise voltages due to M2 and M3, as functions of the pixel readout time  $t_{read}$ . The results are plotted in Figure 4, together with the RMS 1/f noise voltages calculated using the frequency domain method. Assuming the pixel readout time of 1 $\mu$ s, the RMS 1/f noise voltage is about 63 $\mu$ V due to follower transistor, and below 1 $\mu$ V due to access transistor. They are twice as large as the values obtained using frequency domain method. Also plotted in the figure are the noise voltages due to thermal noise. Note that RMS 1/f noise voltage is higher than thermal noise voltage for the follower transistor, but much lower than thermal noise voltage for the access transistor.

Figure 4. Bitline RMS 1/f noise voltage due to M2 (left) and M3 (right).

## 4. 1/F NOISE DUE TO THE RESET TRANSISTOR

Our previous work<sup>9</sup> presented detailed analysis of reset noise due to thermal and shot noise sources. We showed that the reset transistor M1 spends most of the reset time in subthreshold and does not reach steady state in typical APS operation. Thus in analyzing the effect of 1/f noise due to the reset transistor we need to consider not only the nonstationarity of the noise but also the time variability of the circuit.

The Bitline voltage due to the reset transistor 1/f noise at the end of reset is given by<sup>9</sup>

$$V_{M1}(t_r) = a \int_0^{t_r} \frac{I_{M1}(s)}{C_{pd}} e^{-\int_s^{t_r} \frac{g_{m1}(\tau)}{C_{pd}} d\tau} ds,$$

(12)

where  $t_r$  is the reset time,  $I_{M1}(t)$  is the reset transistor M1 1/f noise current,  $g_{m1}(\tau)$  is the transconductance of M1, and a is the amplifying factor of the source follower which is equal to 0.9 in our example circuit. The Bitline mean square reset noise voltage is thus given by

$$\overline{V_{M1}^2(t_r)} = \left(\frac{aq}{AC_{ox}C_{pd}}\right)^2 \int_0^{t_r} \int_0^{t_r} g_{m1}(s_1)g_{m1}(s_2)\mathcal{C}(s_1, |s_2 - s_1|)e^{-\frac{1}{C_{pd}}\int_{s_1}^{t_r} g_{m1}(\tau_1)d\tau_1} e^{-\frac{1}{C_{pd}}\int_{s_2}^{t_r} g_{m1}(\tau_2)d\tau_2} ds_1 ds_2.$$

(13)

Using the MOS transistor subthreshold I-V characteristics, we get that  $g_{m1}(\tau) \approx \frac{C_{pd}}{\tau+\delta}$ , where  $\delta$  is the thermal time<sup>9</sup> and is  $\approx 6$  ns for our example circuit. Thus

$$e^{-\frac{1}{C_{pd}}\int_{s}^{t_{r}}g_{r}(\tau)d\tau} \approx \frac{s+\delta}{t_{r}+\delta}.$$

Substituting this and equation 1 and 4 into equation 13, we get that

$$\overline{V_{M1}^2(t_r)} = a^2 (\frac{q}{AC_{ox}})^2 \frac{1}{(t_r + \delta)^2} \int_0^{t_r} \int_0^{t_r} \int_{\lambda_L}^{\lambda_H} \mathcal{C}_{\lambda}(s_1, |s_2 - s_1|) g(\lambda) d\lambda ds_1 ds_2.$$

(14)

Note that this result is virtually independent of the photodiode capacitance. This of course is very different from the famous  $\frac{kT}{C}$  reset noise due to thermal and shot noise sources.

To compare our results with the commonly used frequency domain method, note that the Bitline mean square noise voltage using the frequency domain method is given by

$$\overline{V_{M1}^2(t_r)} = 2a^2 \int_{\frac{1}{t_r}}^{\infty} \frac{S_{I_d}(f)}{g_{m1}^2(t_r) + 4\pi^2 f^2 C_{pd}^2} df.$$

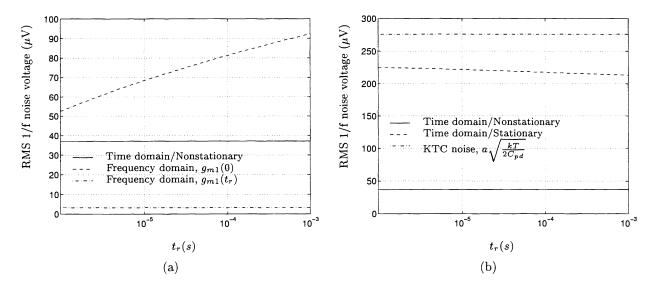

To evaluate this equation we need to decide on the value of  $g_{m1}$  to use. In part a of Figure 5 we plot the results of the frequency domain analysis for two values of  $g_{m1}$ , one at the beginning and the other at the end of the reset time. Note the enormous difference between the curves for the two  $g_{m1}$  values. This presents a serious problem with using the frequency domain method. Depending on which  $g_{m1}$  value is used, the results can vary from  $3.2\mu$ V to  $68\mu$ V at  $t_r = 10\mu$ s ! Also plotted in that figure is the results calculated using equation 14. Note that the shape of the time domain curve is very similar to that of the frequency domain curve assuming the  $g_{m1}$  value at the end of reset. However, the difference between the two curves is very substantial (over 11X).

To isolate the effect of using the stationary versus the nonstationary noise models, in part b of Figure 5 we plot the curves using the stationary noise model and our nonstationary version, applying the same time varying circuit model for both. In calculating the noise assuming the stationary model we simply replace the  $C_{\lambda}(s_1, |s_2 - s_1|)$  in equation 14 by the stationary autocovariance  $C_{\lambda}(|s_2 - s_1|)$ . As can be seen from the two curves, the RMS noise voltage using the stationary model is much higher, e.g.,  $222\mu V$  versus  $37.2\mu V$  at  $t_r = 10\mu s$ . The often cited KTC noise due to reset transistor shot noise  $a\sqrt{\frac{kT}{2C_{pd}}}$  is plotted and is

around  $276\mu$ V. Note that the RMS 1/f noise voltage predicted by the stationary model is comparable to this KTC noise, whereas experiments<sup>9</sup> suggested that KTC noise dominates reset noise. This demonstrates the validity and the importance of using our nonstationary 1/f noise model to calculate 1/f noise power of dynamic circuits.

Figure 5. Simulated bitline referred RMS 1/f reset noise: (a) Frequency domain versus time domain. (b) Stationary 1/f noise model versus the nonstationary extension, both assuming time varying circuit model.

#### 5. CONCLUSION

We described a new method for the analysis of 1/f noise in MOS circuits based on a nonstationary extension of the physical model of 1/f noise in MOS transistors and time domain analysis. We used the new method to provide accurate estimates of the effect of 1/f noise due to the pixel level transistors in a CMOS APS. We found that the commonly used frequency domain analysis method can produce very inaccurate estimates for the RMS 1/f noise voltage.

The 1/f noise model discussed also reveals an important fact about the effect of correlated double sampling (CDS) on 1/f noise in image sensors. CDS, which is performed by taking two samples, one with and one without the signal, is often used to suppress noise in analog circuits.<sup>14</sup> In a circuit operated in the small signal regime, *e.g.*, an op-amp, the traps responsible for generating the 1/f noise in the two samples are the same. As a result, the 1/f noise components of the two samples are highly correlated, and 1/f noise can be suppressed. When performing CDS in an image sensor, the 1/f noise components of the two samples can be highly uncorrelated, since the circuit is not necessarily operated in small signal regime. The traps responsible for the 1/f noise generated during normal readout and during reset readout can be at different energy levels, resulting in uncorrelated noise processes. Consequently, CDS does not necessarily suppress 1/f noise, and may indeed increase it.

#### ACKNOWLEDGEMENTS

The work reported in this paper was partially supported under the Programmable Digital Camera Program by Intel, HP, Kodak, Interval Research, and Canon. The authors would like to thank T. Chen, H. Lim, X. Liu, and K. Salama for helpful discussions.

## REFERENCES

- 1. C. Hu, G. P. Li, E. Worley, and J. White, "Consideration of Low-Frequency Noise in MOSFET's for Analog Performance," *IEEE Electron Device Letters* 17, pp. 552–554, December 1996.

- 2. F. N. Hooge, "1/f Noise Sources," IEEE Trans. Electron Device 41, pp. 1926-1935, November 1994.

- 3. L. K. J. Vandamme, X. Li, and D. Rigaud, "1/f Noise in MOS Devices, Mobility or Number Fluctuations?," *IEEE Trans. Electron Device* 41, pp. 1936–1944, November 1994.

- M. J. Kirton and M. J. Uren, "Noise in Solid-State Microstructures: A New Perspective on Individual Defects, Interface States and Low-frequency (1/f) Noise," Advances in Physics 38(4), pp. 367–468, 1989.

- 5. K. K. Hung, C. Hu, and Y. C. Cheng, "Random Telegraph Noise of Deep-Submicrometer MOSFETS's," *IEEE Electron Device Letters* 11, pp. 90–92, February 1990.

- K. K. Hung, P. K. Ko, C. Hu, and Y. C. Cheng, "A Unified Model for the Flicker Noise in Metal-Oxide-Semiconductor Field-Effect Transistors," *IEEE Trans. Electron Device* 37, pp. 654–665, March 1990.

- J. Chang, A. A. Abidi, and C. R. Viswanathan, "Flicker Noise in CMOS Transistors from Subthreshold to Strong Inversion at Various Temperatures," *IEEE Trans. Electron Device* 41, pp. 1965–1971, November 1994.

- 8. C. Jakobson, I. Bloom, and Y. Nemirovsky, "1/f Noise in CMOS Transistors for Analog Applications From Subthreshod to Saturation," *Solid-State Electronics* 42(10), pp. 1807–1817, 1998.

- 9. H. Tian, B. Fowler, and A. El Gamal, "Analysis of Temporal Noise in CMOS APS," in *Proc. SPIE*, vol. 3649, pp. 177–185, (San Jose, CA), Jan. 1999.

- 10. A. van der Ziel, Noise in Solid State Devices and Circuits, Wiley, 1986.

- T. Boutchacha, G. Ghibaudo, G. Guegan, and T. Skotnicki, "Low Frequency Noise Characterization of 0.18um Si CMOS Transistors," *Microelectron. Reliab.* 37(10/11), pp. 1599–1602, 1997.

- 12. H. Tian and A. El Gamal, "Time Domain Analysis of 1/f noise in MOS circuits," In Preparation.

- 13. E. Simoen and C. L. Claeys, "On the Geometry Dependence of the 1/f Noise in CMOS Compatible Junction Diodes," *IEEE Trans. Electron Device* 46, pp. 1725–1732, August 1999.

- C. C. Enz and G. C. Temes, "Circuit Techniques for Reducing the Effects of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization," Proc. IEEE 84, pp. 1584–1614, November 1996.